SPECIAL HANDLING

LTV ELECTROSYSTEMS, INC. Garland Division P. O. Box 6118 Dallas, Texas 75222

784106 CY 24 700 PAGES

PRELIMINARY

REAPER ENGINEERING ANALYSIS REPORT

52000-R500 **DEC** 29 January 1967

Approved By  $\mathcal{M}$ .

mrB

Program Manager

700 No. of Pages

Approved by  $\underbrace{C}_{E. G. Ke}$

Director -

Special Projects Dept.

8 ml (2) 2 B -163-70

Approved for Release: 2017/08/16 C05099935

## SPECIAL HANDLING

52000-R500 Page ii

| REV.     | DAT         | E | REV. BY                                | PAGES AFFECTED | REMARKS          |

|----------|-------------|---|----------------------------------------|----------------|------------------|

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          | :           |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   | -                                      |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   | · · · · · · · · · · · · · · · · · · ·  | ,              |                  |

| -+       | <del></del> |   |                                        |                |                  |

| -        |             |   | ************************************** |                |                  |

| -+       |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          | <del></del> |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

| _        |             |   | - F                                    |                |                  |

| -        |             |   |                                        |                |                  |

|          |             |   | 1- T                                   |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                | }                |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

| $\neg +$ |             |   |                                        |                |                  |

| -+       |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        | A-1            |                  |

|          |             |   | A.,,                                   |                |                  |

|          |             |   |                                        |                |                  |

|          |             |   |                                        |                |                  |

| 1        |             |   |                                        | SPECIAL HANDL  | HANDLY ON COUNTY |

SPECIAL HANDLING

Approved for Release: 2017/08/16 C05099935

50X1

SPECIAL HANDLING

52000-R500 Page iii

#### TABLE OF CONTENTS

| Paragraph<br>Number |                                     | Pa |

|---------------------|-------------------------------------|----|

|                     | LIST OF FIGURES                     | xi |

|                     | LIST OF TABLES                      | XX |

| 1.0                 | INTRODUCTION                        |    |

| 1.1                 | Scope                               |    |

| 1.2                 | Summary                             |    |

| 2.0                 | SYSTEM DESCRIPTION                  |    |

| 2.1                 | EOB Function                        |    |

| 2.1.1               | Frequency Coverage                  |    |

| 2.1.2               | Ground Coverage                     |    |

| 2.1.3               | Sensitivity                         |    |

| 2.1.4               | Signal Processing                   |    |

| 2.2                 | Technical Intelligence Functions    | 1  |

| 2.2.1               | Recognition Mode Signal Processing. | 1  |

| 2.2.2               | Predetected Signal Output           | 1  |

| 2.2.3               | Marker Word                         | 1  |

| 2.3                 | Operation                           | 1  |

| 2.3.1               | EOB Readin                          | 1  |

| 2.3.2               | EOB/TI Readin                       | 3  |

| 2.3.3               | Memory Load                         | 3  |

| 2.4                 | Digital Data Word Formats           | 4  |

| 2.4.1               | EOB Digital Data                    | 24 |

| 2.4.2               | TI Marker Words                     | 24 |

| 2.4.3               | Memory Load and Readout Formats     | 4  |

CH COLDER

HANDLE VIA BYEMAN O VIROL SYSBEM ONLY 50X1

SPECIAL HANDLING

Approved for Release: 2017/08/16 C05099935

50X1

### Approved for Release: 2017/08/16 C05099935

# SPECIAL HANDLING

52000-R500 Page iv

#### TABLE OF CONTENTS (Continued)

| Paragraph<br>Number |                                    | Page |

|---------------------|------------------------------------|------|

| 2.5                 | Performance Specifications Summary | 46   |

| 2.5.1               | Frequency Coverage                 | 46   |

| 2.5.2               | Field of View                      | 46   |

| 2.5.3               | D/F Accuracy                       | 47   |

| 2.5.4               | Scan Parameters                    | 47   |

| 2.5.5               | Sensitivity                        | 48   |

| 2.5.6               | Dynamic Range                      | 48   |

| 2.5.7               | Recognizer                         | 48   |

| 2.5.8               | Pre-Detected Signal Output         | 51   |

| 2.5.9               | CW Operation                       | 52   |

| 2.5.10              | Buffer Storage                     | 52   |

| 2.5.11              | Measurement Capabilities           | 53   |

| 2.5.12              | Digital Word Formats               | 55   |

| 2.5.13              | False Data                         | 55   |

| 2.5.14              | Orbital Lifetime                   | 56   |

| 3.0                 | SYSTEM ANALYSIS                    | 57   |

| 3.1                 | Introduction                       | 57   |

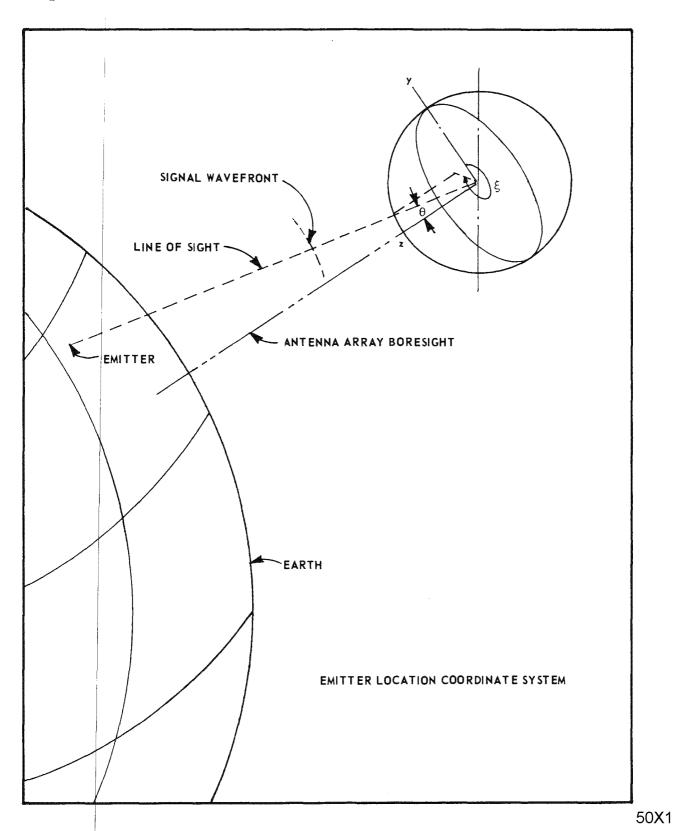

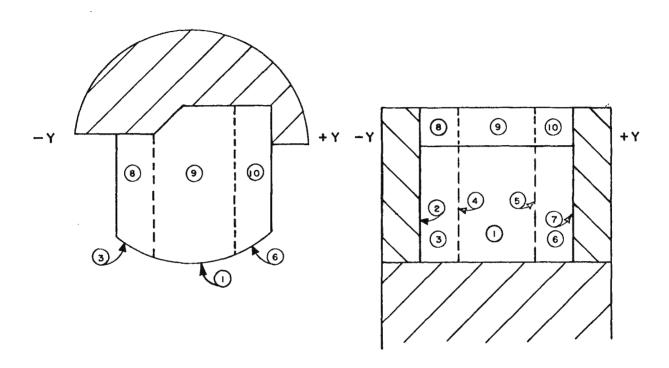

| 3.2                 | Coordinate Geometry                | 57   |

| 3.2.1               | Emitter Location Coordinate System | 57   |

| 3.3.3               | Restricted Field of View           | 59   |

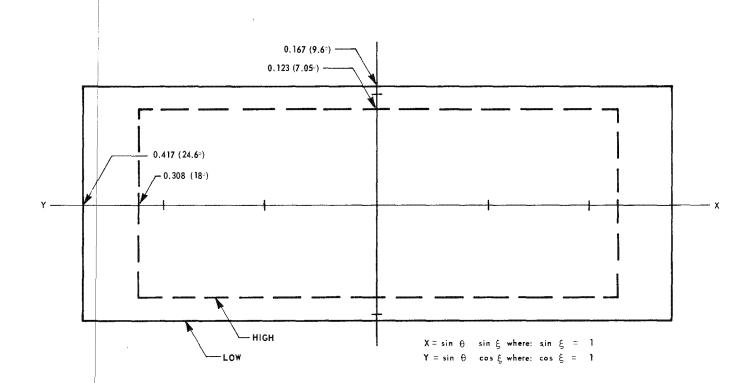

| 3.2.3               | Field-of-View Earth Coverage       | 60   |

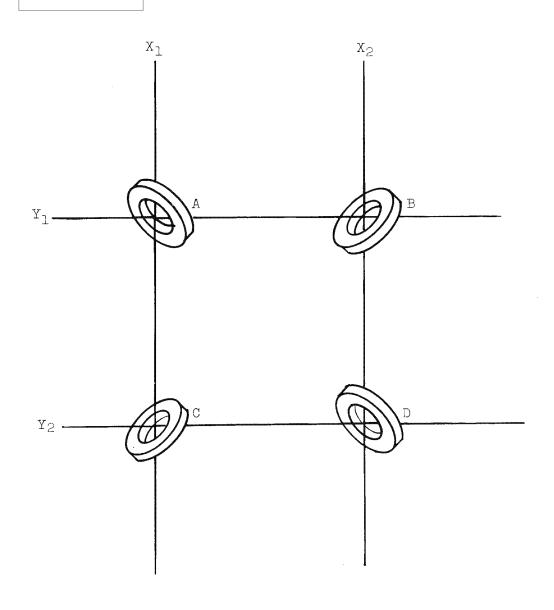

| 3.3                 | Antenna Phase Response             | 62   |

| 3.3.1               | Antenna Array Phase Rotations      | 62   |

# Approved for Release: 2017/08/16 C05099935 SPECIAL HANDLING

52000-R500 Page v

#### TABLE OF CONTENTS (Continued)

| Paragi<br>Numbei |                                       | Page |

|------------------|---------------------------------------|------|

| 3.3.3            | Ambiguity Removal Technique           | 66   |

| 3.4              | Antenna Ambiguity Response            | 68   |

| 3.5              | Receiver Characteristics              | 71   |

| 3.5.1            | System Noise Figure                   | 71   |

| 3.5.2            | Equivalent Input Thermal Noise Power  | 72   |

| 2.5.3            | Minimum Signal-to-Noise Ratio         |      |

| 3.5.4            | Real/Image Signal Identification and  |      |

|                  | Spurious Rejection Circuitry          | 74   |

| 3.6              | Error Analysis                        | 77   |

| 3.6.1            | Phase Error                           | 77   |

| 3.6.2            | Location Accuracy                     | 77   |

| 3.6.3            | False Alarm Rate                      | 79   |

| 3.6.4            | Amplitude Error                       | 83   |

| 3.6.5            | Pulse Repetition Interval Error       | 8 5  |

| 3.6.6            | Pulse Width Error                     | 8 5  |

| 3.6.7            | Frequency Error                       | 86   |

| 3.7              | Reaper Effective Sensitivity to Three |      |

|                  | Emitters of Interest As A Function of |      |

|                  | Location                              |      |

| 4.0              | DESIGN                                | 92   |

| 4.1              | Antennas                              | 91   |

| 4.1.1            | Requirements                          | 9    |

52000-R500 Page vi

SPECIĂL HÂNDLING

#### TABLE OF CONTENTS (Continued)

| Paragraph<br>Number |                                      | Page |

|---------------------|--------------------------------------|------|

| 4.1.2               | Design Consideration                 | 92   |

| 4 1.3               | Development                          | 99   |

| 4.1.4               | Summary of Technical Specifications  | 100  |

| 4.2                 | RF Assembly                          | 114  |

| 4.2.1               | Introduction                         | 114  |

| 4.2.2               | RF Bandpass Filters                  | 116  |

| 4.2.3               | RF Checkout Board (RFCO)             | 119  |

| 4.2.4               | Main Stripline (Mixers)              | 130  |

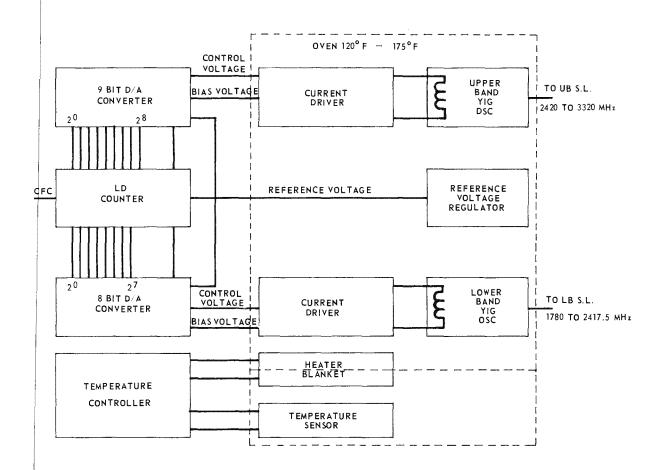

| 4.3                 | Local Oscillator Assembly            | 143  |

| 4.3.1               | Introduction                         | 143  |

| 4.3.2               | Description of Operation             | 145  |

| 4.3.3               | YIG Oscillators                      | 148  |

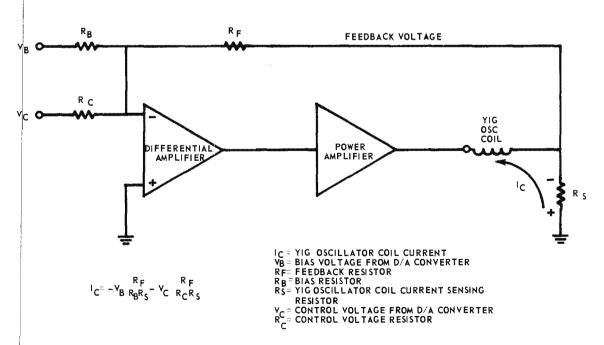

| 4.3.4               | Current Driver                       | 150  |

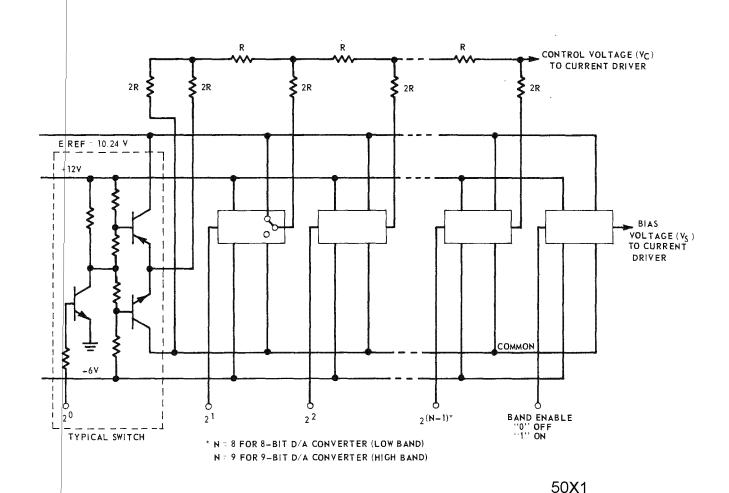

| 4.3.5               | Digital-to-Analog (D/A) Converters   | 154  |

| 4.3.6               | Reference Voltage Regulator          | 155  |

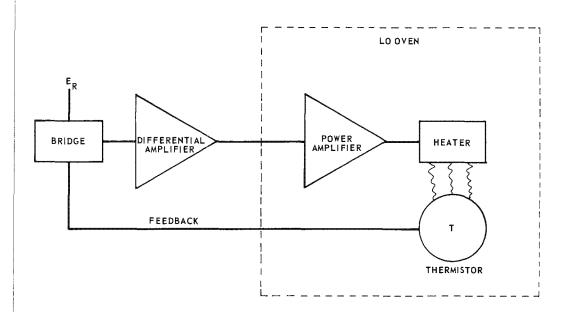

| 4.3.7               | Temperature Controller               | 158  |

| 4.4                 | RF Calibrator                        | 160  |

| 4.4.1               | Introduction                         | 160  |

| 4.4.2               | Design                               | 1ć2  |

| 4.5                 | Intermediate Frequency (IF) Assembly | 166  |

| 4.5.1               | Introduction                         | 166  |

| 4.5.2               | Preamplifier Subassemnly             | 170  |

50X1 PANTAGE STORES COM

# SPECIAL HANDLING

#### TABLE OF CONTENTS (Continued)

| Paragraph<br>Number |                                            | Page  |

|---------------------|--------------------------------------------|-------|

| 4.5.3               | Signal Combiner Subassembly                | 171   |

| 4.5.4               | Hybrid Subassembly                         | 174   |

| 4.5.5               | Preamplifier Switch Subassembly            | 177   |

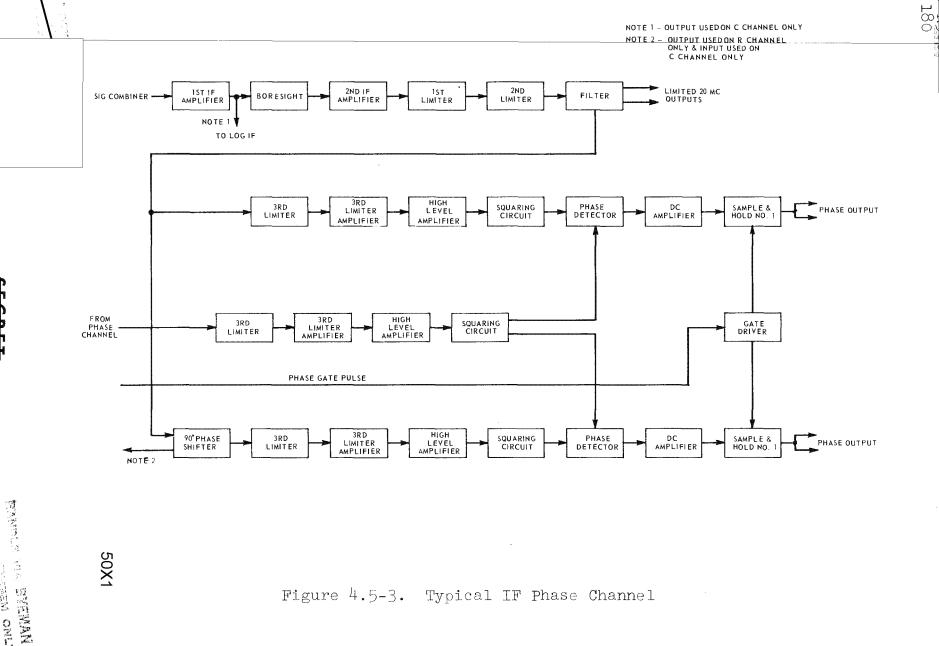

| 4.5.6               | Intermediate Frequency (IF) Phase          |       |

|                     | Channels (51000)                           | 178   |

| 4.5.7               | Intermediate Frequency (IF) Phase          |       |

|                     | Channels (51100)                           | 196   |

| 4.5.8               | IF Frequency Confirm Channel               | 198   |

| 4.5.9               | Log IF Amplifier                           | 203   |

| 4.5.10              | Signal-Indicate Generator                  | 211   |

| 4.5.11              | Amplitude Ratio and Pulse Width Comfirm    |       |

|                     | Subassembly                                | 219   |

| 4.5.12              | Real and Image Logic Subassembly           | 227   |

| 4.5.13              | Tone Tag Signal (TTS) Subassembly          | 237   |

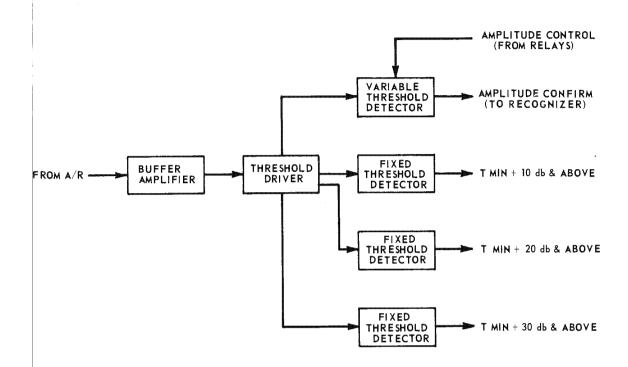

| 4.5.14              | Recognizer Amplitude Threshold Subassembly | z 246 |

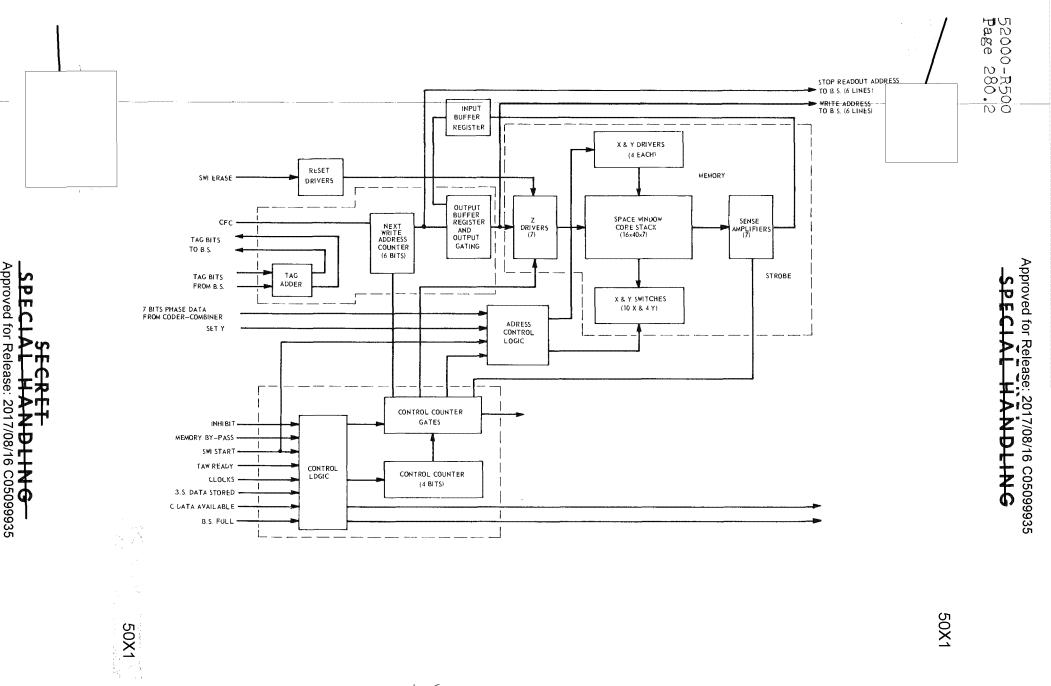

| 4.6                 | Data Handler                               | 260   |

| 4.6.1               | Introduction                               | 260   |

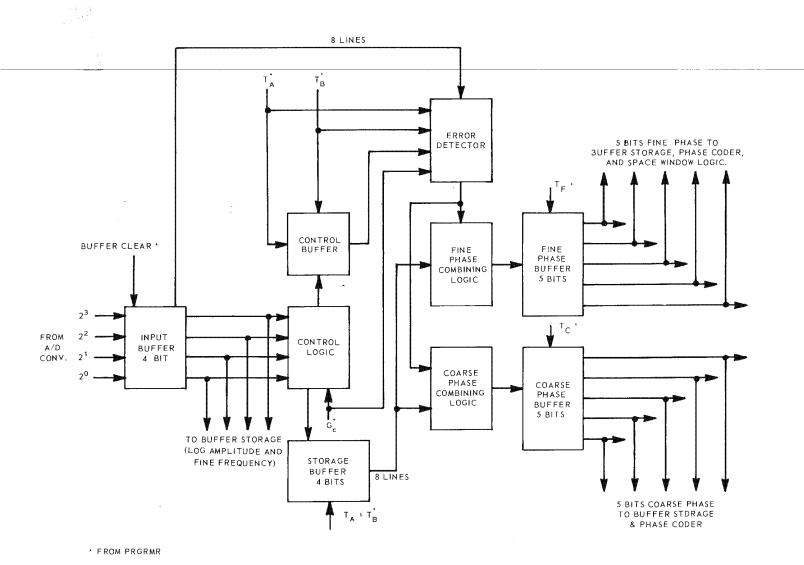

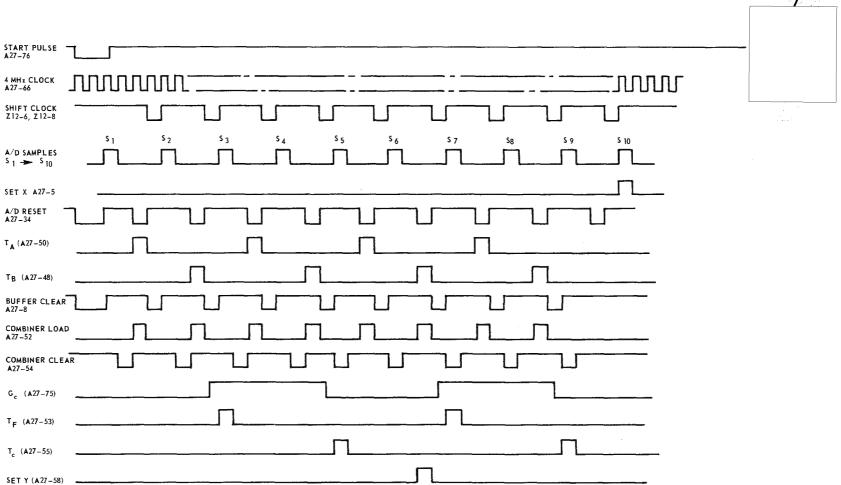

| 4.6.2               | Phase Combiner                             | 264   |

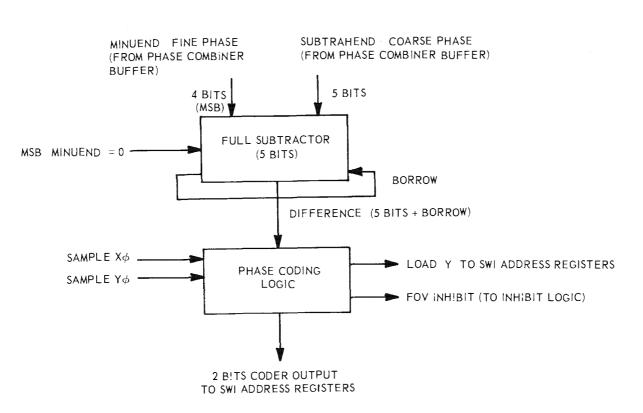

| 4.6.3               | Phase Coder                                | 274   |

| 4.6.4               | Space Window Logic                         |       |

| 4.6.5               | Inhibit Logic                              |       |

| 4.6.6               | Programmer                                 |       |

| 4.6.7               | PRI Encoder                                |       |

SPECIAL HANDLING Approved for Release: 2017/08/16 C05099935 50X1

MARGIN WAS TREET, C WITT CYSTERS CLER

#### SPECIAL HANDLING

52000-R500 Page viii

#### TABLE OF CONTENTS (Continued)

|    | ragraph<br>mber |                               | Page |

|----|-----------------|-------------------------------|------|

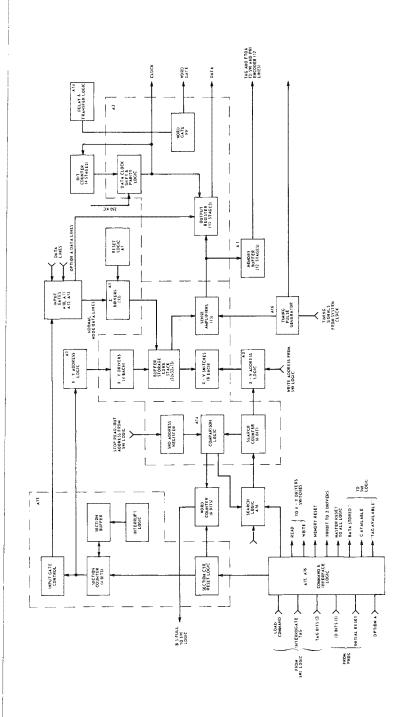

| 4. | 6.8             | Buffer Storage Logic          | 281  |

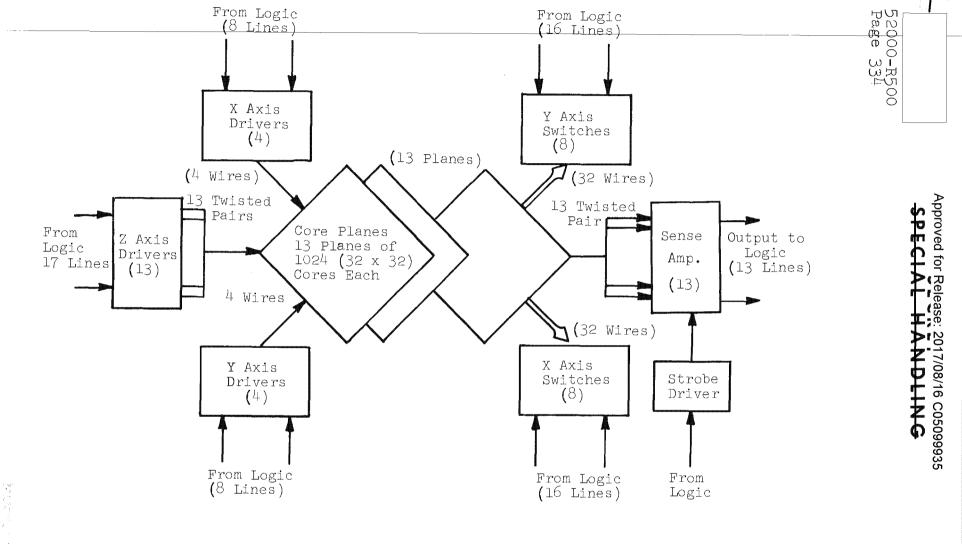

| 4. | 6.9             | Memories                      | 317  |

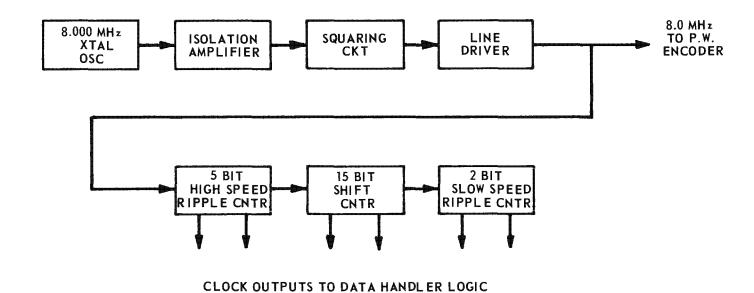

| 4. | 6.10            | System Clock                  | 339  |

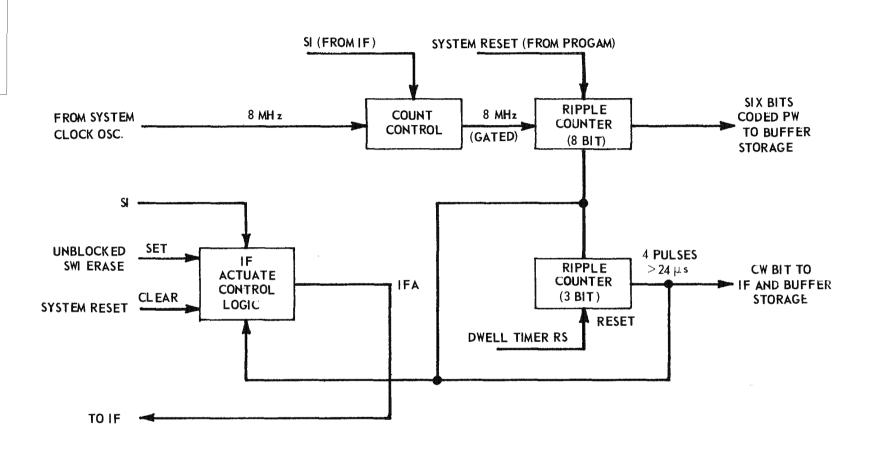

| 4. | .6.11           | Pulse Width Encoder           | 343  |

| 4. | 6.12            | Time Encoder                  | 347  |

| 4. | 6.13            | Attitude Encoder              | 348  |

| 4  | 6.14            | Test Generator Logic          | 356  |

| 4  | 6.15            | Data Handler Interface        | 361  |

| 4  | 6.16            | Marker Word Generator         | 366  |

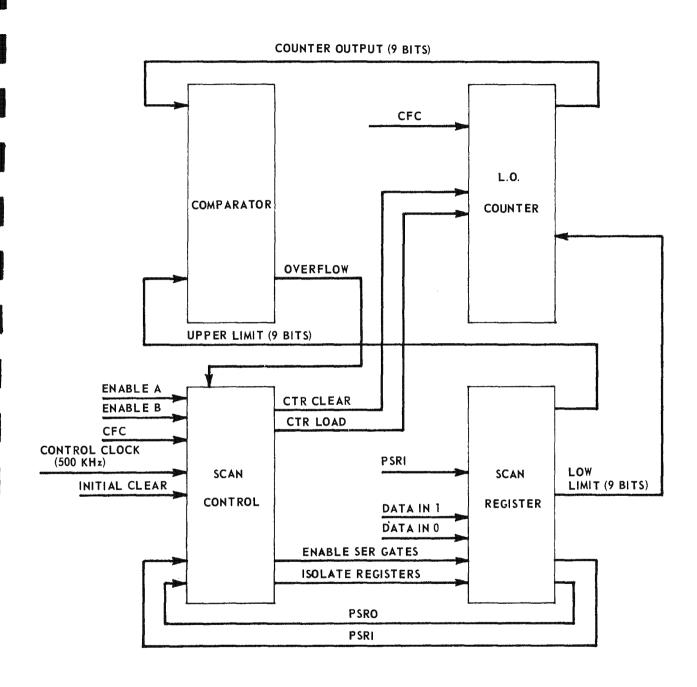

| 4  | 6.17            | Scan Control Logic            | 374  |

| 4  | 6.18            | Relay Assembly                | 383  |

| 4  | 6.19            | Telemetry Unit                | 390  |

| 4  | 7               | Recognizer                    | 406  |

| 4  | 7.1             | Introduction                  | 406  |

| 4  | .7.2            | Theory Of Operation           | 407  |

| 4  | .7.3            | Detailed Logic Description    | 415  |

| 4  | .8              | Power Supply                  | 459  |

| 4  | .8.1            | Introduction                  | 459  |

| 4  | .8.2            | Control Circuitry             | 461  |

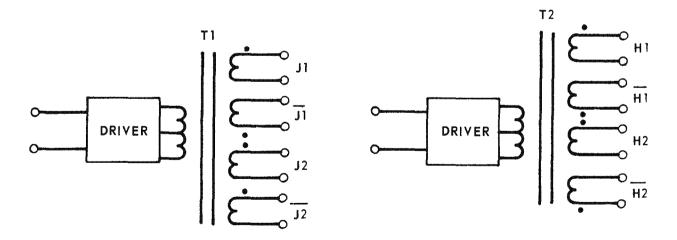

| 4  | .8.3            | Driver Circuitry              | 465  |

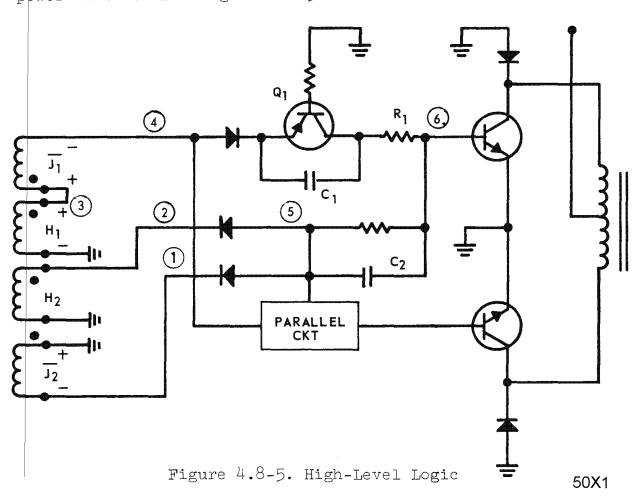

| 4  | .8.4            | High Level Logic Circuitry    | 466  |

| 4  | .8.5            | Output Stage                  | 469  |

| 4  | .8.6            | Reference and Error Amplifier | 469  |

Author and Blesser

52000-R500 Page ix

### TABLE OF CONTENTS (Continued)

| Paragraph<br>Number |                                         | Page |

|---------------------|-----------------------------------------|------|

| 4.8.7               | Auxiliary Power Supply                  | 469  |

| 4.8.8               | Voltage Monitor                         | 470  |

| 4.8.9               | Current Monitor                         | 472  |

| 4.8.10              | EMl Filters                             | 472  |

| 4.8.11              | Voltage Regulators                      | 472  |

| 4.8.12              | Power Supply Performance                | 474  |

| 4.9                 | Mechanical Design                       | 481  |

| 4.9.1               | Introduction                            | 481  |

| 4.9.2               | Common Base Plate and Support Structure | 481  |

| 4.9.3               |                                         |      |

| 4.9.4               | IF Section and A/D Converter            | 487  |

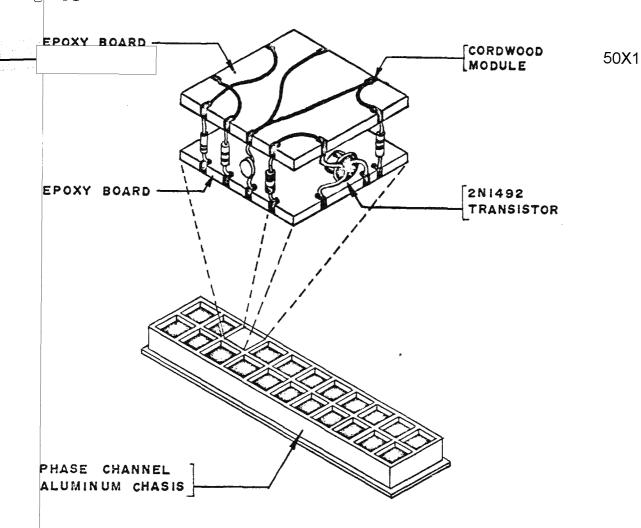

| 4.9.5               | Data Handlers                           | 491  |

| 4.9.6               | Memories                                | 493  |

| 4.9.7               |                                         |      |

| 4.9.8               | Main Stripline Assemblies               | 497  |

| 4.9.9               |                                         |      |

| 4.9.10              |                                         |      |

| 4.9.11              | RF System Calibrator                    | 501  |

| 4.9.12              | IF Preamplifiers                        | 501  |

| 4.9.13              | Power Supply                            | 501  |

| 4.9.14              | Power Distribution Assembly             | 504  |

| 4.9.15              | Relay Assembly                          | 504  |

| 4.9.16              | T/M Assembly                            | 507  |

FERRITA DATE STORY COMPANA. PRIMADO KARLET

### SPECIĂL HÂNDLING

52000-R500 Page x

#### TABLE OF CONTENTS (Continued)

| Paragraph<br>Number |                                 | Page                                                   |

|---------------------|---------------------------------|--------------------------------------------------------|

| 4.9.17              | Mechanical Specifications       | 507                                                    |

| 4.10                | Thermal Design                  | 510                                                    |

| 4.10.1              | Introduction                    | 510                                                    |

| 4.10.2              | System Thermal Characteristics  | 511                                                    |

| 4.10.3              | System Thermal Analysis         | 516                                                    |

| 4.10.4              | Individual Hot Spot Analysis    | 524                                                    |

| 4.11                | Electromagnetic Interference Co | ontrol 550                                             |

| 4.11.1              | Introduction                    | 550                                                    |

| 4.11.2              | Purpose                         | 550                                                    |

| 4.11.3              | General EMI Control Concepts    | 550                                                    |

| 4.11.4              | EMI Test Program                | 553                                                    |

| 5.0                 | TEST PROGRAM                    | 555                                                    |

| 5 1                 | Introduction                    | 555                                                    |

| 5 2                 | Classification of Tests         | 555                                                    |

| 5.2.1               | Receiving Inspection            | 555                                                    |

| 5 2.2               | Parts Conditioning              | 555                                                    |

| 5.2.3               | Developmental Testing           | 556                                                    |

| 5.2.4               | Subassembly and Assembly Testi  | ng 558                                                 |

| 5.2.5               | Qualification Test              | 570                                                    |

| 5.2.6               | Acceptance Test                 | 573                                                    |

| 5.3                 | Documentation                   | 574                                                    |

| 6.0                 | RELIABILITY PROGRAM             | 582                                                    |

| 6 1                 | Introduction Factors Courses    | 582<br>**** <b>\$</b> ******************************** |

SPECIAL HANDLING

Approved for Release: 2017/08/16 C05099935

52000-R500 Page xi

#### TABLE OF CONTENTS (Continued)

| Þaragraph<br>Number |                                   | Page |

|---------------------|-----------------------------------|------|

| 6.2                 | Reliability Requirements          | 582  |

| 6.2.1               | Reference Documents               | 582  |

| 6.3                 | Reliability Implementation        | 583  |

| 6.3.1               | Parts Control                     | 583  |

| 6.3.2               | Design Reviews                    | 584  |

| 6.3.3               | Subcontractor Control             | 585  |

| 6.3.4               | Limited Life Items                | 585  |

| 6.3.5               | Trouble and Failure Reporting     | 586  |

| 6.3.6               | Log Books                         | 586  |

| 6.3.7               | Reliability and Quality Assurance |      |

|                     | Interfaces                        | 587  |

| 6.4                 | Reliability Estimate              | 587  |

| 6.4.1               | Module Failure Rates              | 588  |

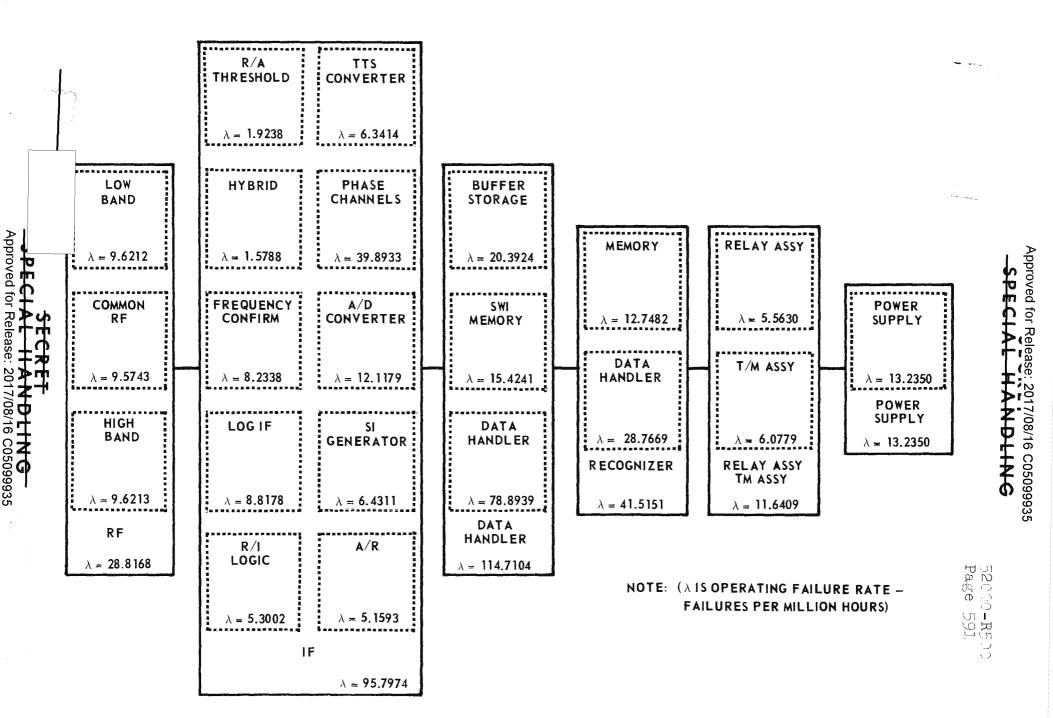

| 6.4.2               | Reliability Diagram               | 588  |

| 6.4.3               | System MTBF                       | 588  |

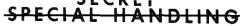

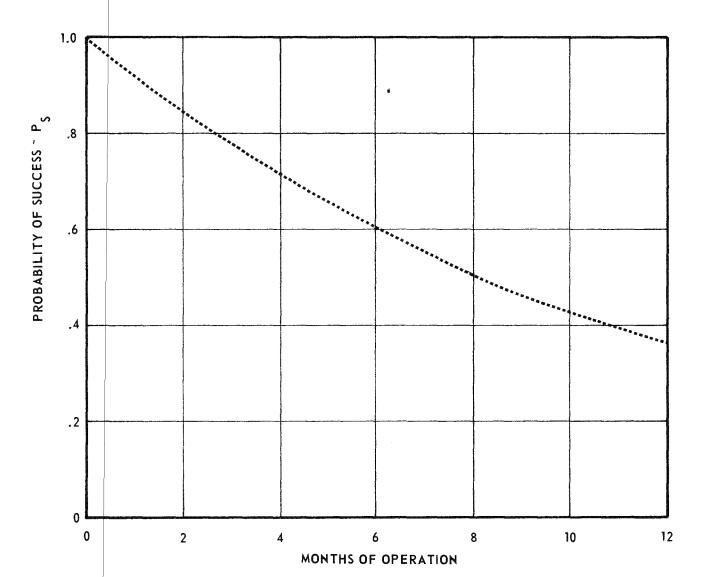

| 6.4.4               | Probability of Survival           | 592  |

| 6.5                 | Summary and Conclusions           | 593  |

| 7.0                 | GROUND SUPPORT AND TEST EQUIPMENT | 598  |

| 7.1                 | Functional Description            | 598  |

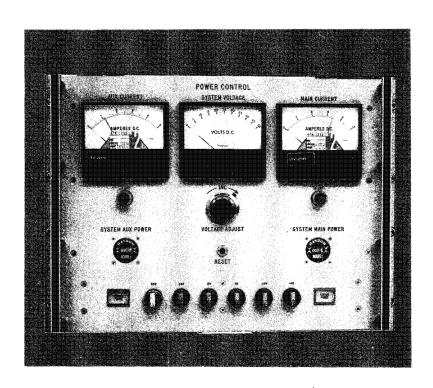

| 7.1.1               | Power Control                     | 599  |

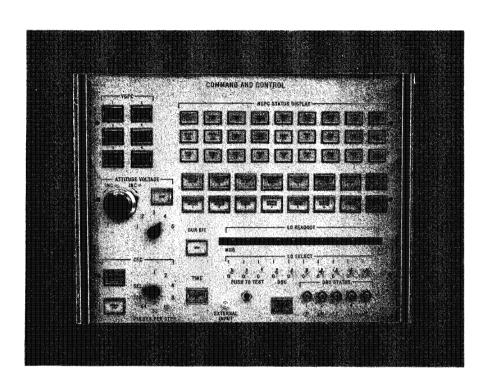

| 7.1.2               | Command and Control               | 601  |

| 7.1.3               | Data Monitoring                   | 612  |

| 7.1.4               |                                   |      |

Manley via 6757946 Control system only

THE ENGLISH

50X1

SPECIAL HANDLING

Approved for Release: 2017/08/16 C05099935

52000-R500 Page xii

#### TABLE OF CONTENTS (Continued)

|    | ragraph<br>mber |                                        | Page |

|----|-----------------|----------------------------------------|------|

| 7. | 1.5             |                                        |      |

| 7. | 1.6             | Error Detecting                        | 620  |

| 7  | 1.7             | Recognizer/Partial Scan Memory Loading | 621  |

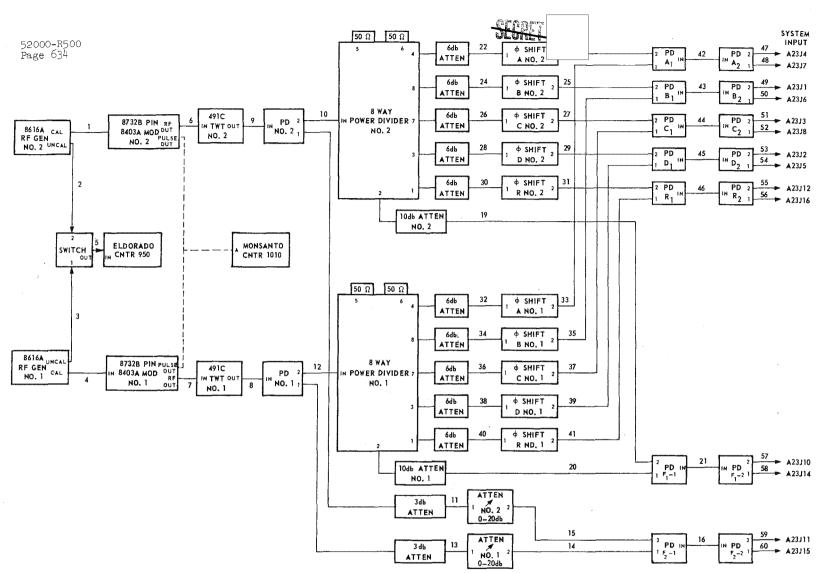

| 7  | 1.8             | RF Signal Input                        | 623  |

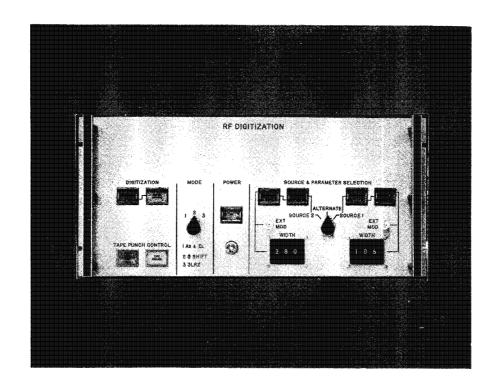

| 7  | 1.9             | RF Parameter Digitization              |      |

| 7  | 1.2             |                                        |      |

| 2  | .2.1            |                                        |      |

| 2  | .2.2            |                                        |      |

| 2  | .2.3            | Printer                                | 632  |

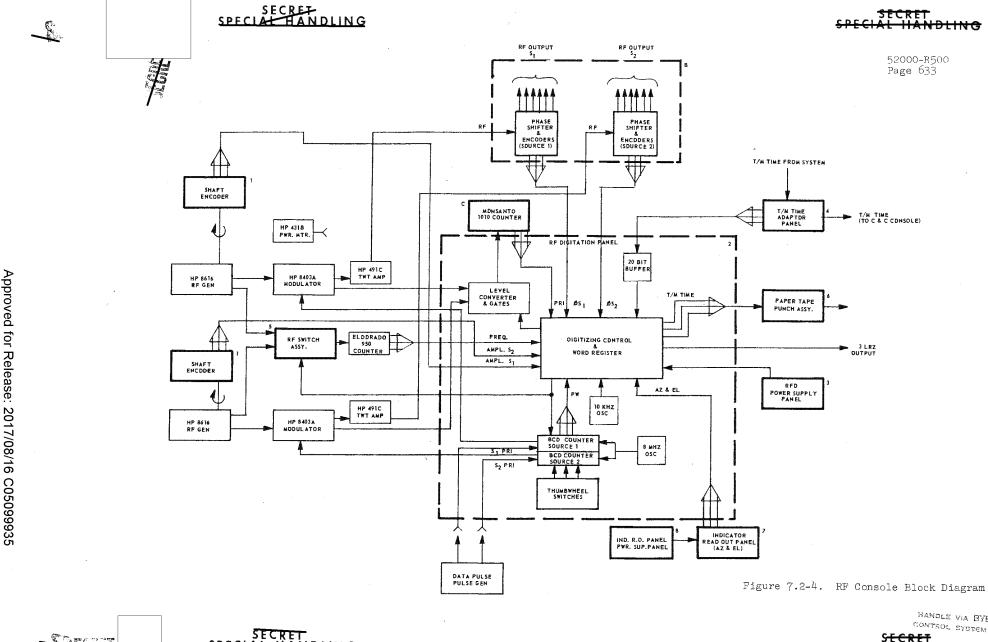

| 7  | .2.4            | RF Console                             | 632  |

| 7  | <b>,2,</b> 5    | Positioner and Positioner Control      | 632  |

52000-R500 Page xiii

#### LIST OF FIGURES

| Figure No.              | Title                                  | Page |

|-------------------------|----------------------------------------|------|

| 1.1-1                   | Reaper                                 |      |

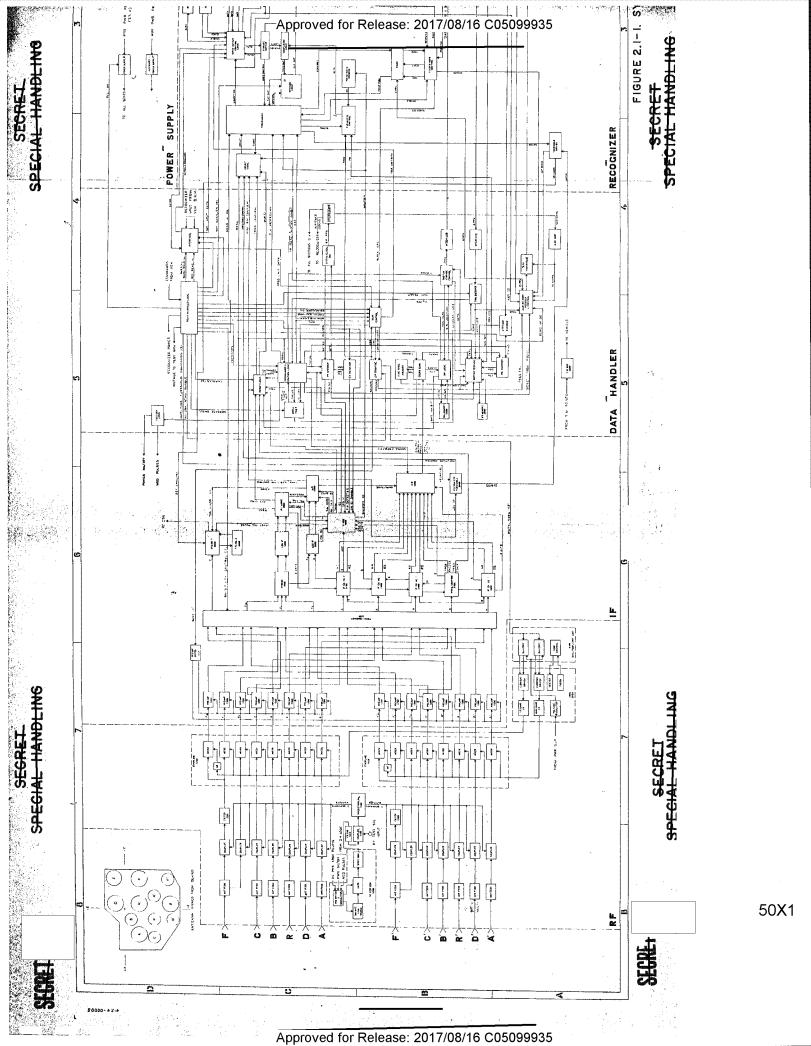

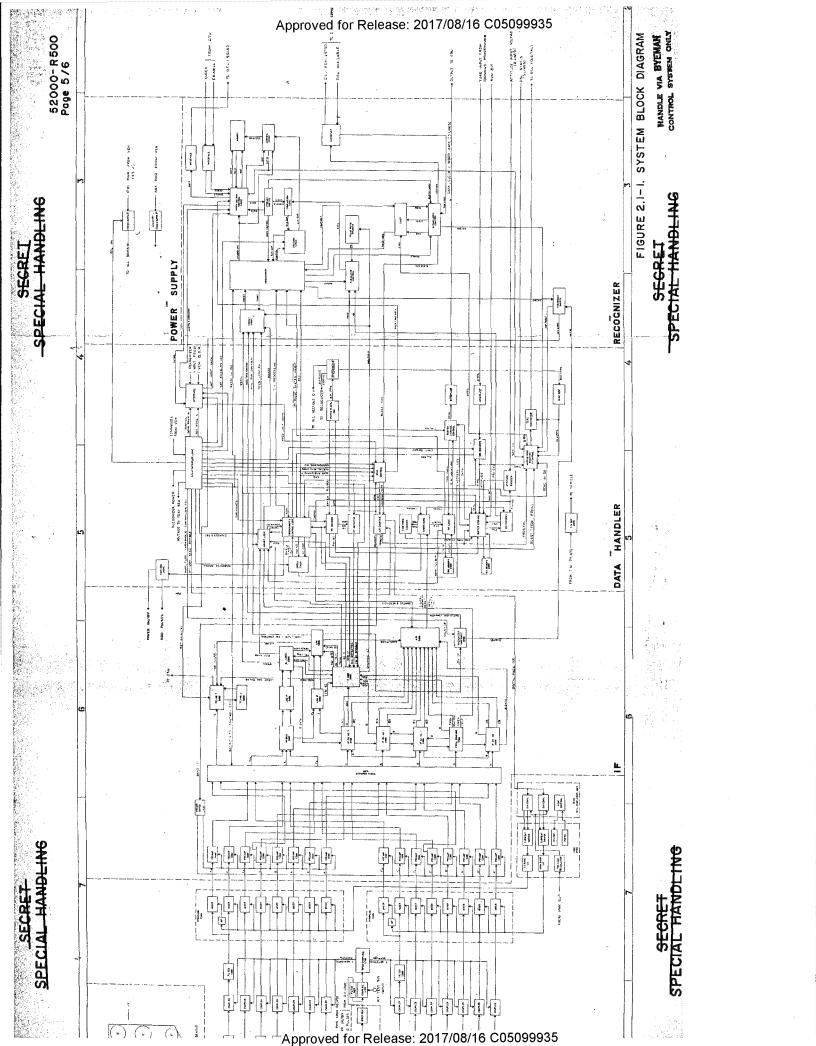

| 2.1-1                   | System Block Diagram                   | 5/6  |

| 2.1-2                   | Frequency Coverage                     | 7    |

| 2.1-3                   | Scan Time                              | 9    |

| 2.1-4                   | Field-of-View Inhibit Circle           | 10   |

| 2.1-5                   | Threshold ERP                          | 11   |

| 2.2-1                   | Predetector Amplitude Response Curves  | 16   |

| 2.2-2                   | Predetector Signal Characteristics     | 17   |

| 3.2-1                   | Emitter Location Coordinate System     | 58   |

| 3.2-2                   | System Field-of-View                   | 60   |

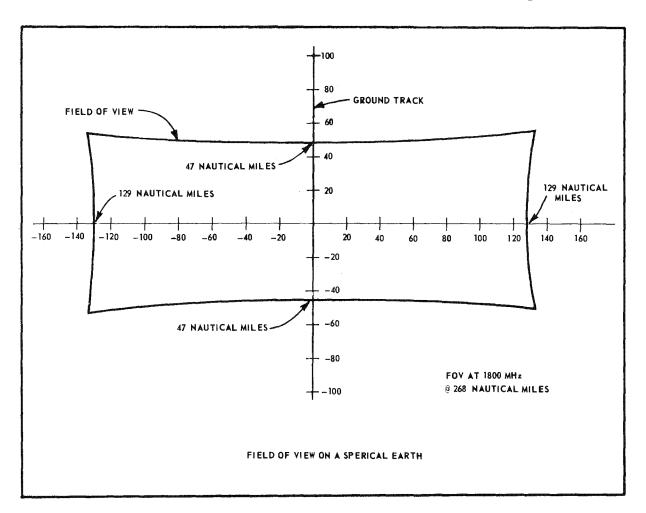

| 3.2-3                   | Field-of-View On A Spherical Earth     | 61   |

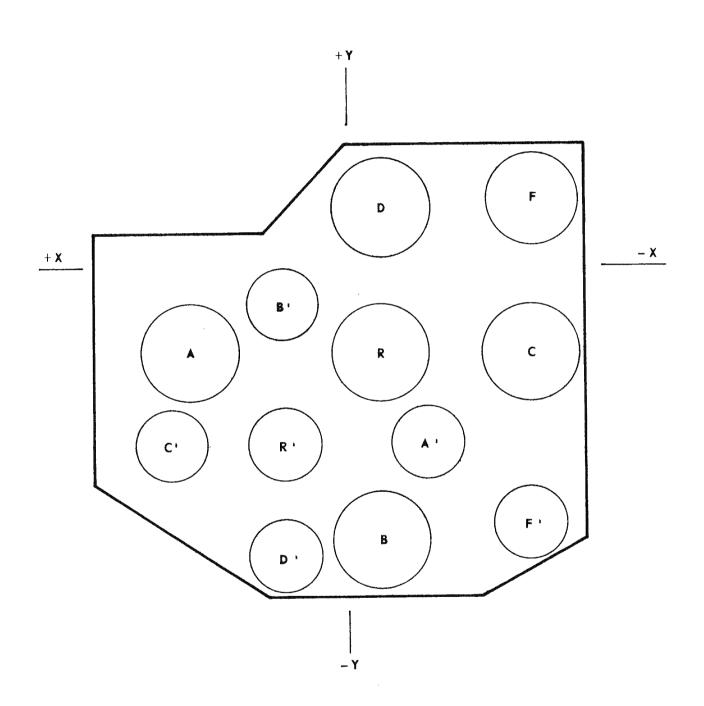

| 3.3-1                   | Antenna Array                          | 63   |

| 3.3-2                   | Phase Field-of-View                    | 65   |

| 3.3-3                   | Horizon-to-Horizon Phase Relationships | 67   |

| 3.3-4                   | Unambiguous Phase Grouping             | 67   |

| 3.4-1                   | Mode 2 Spiral Phase Response           | 72   |

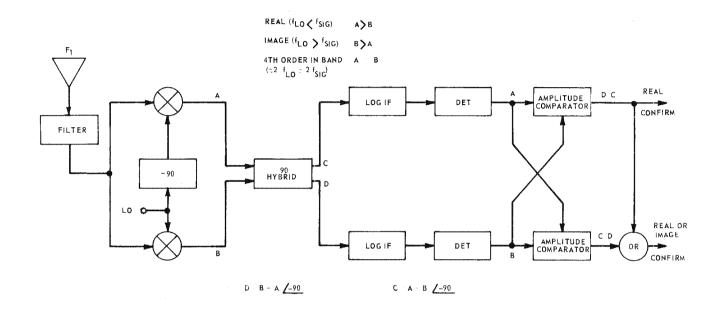

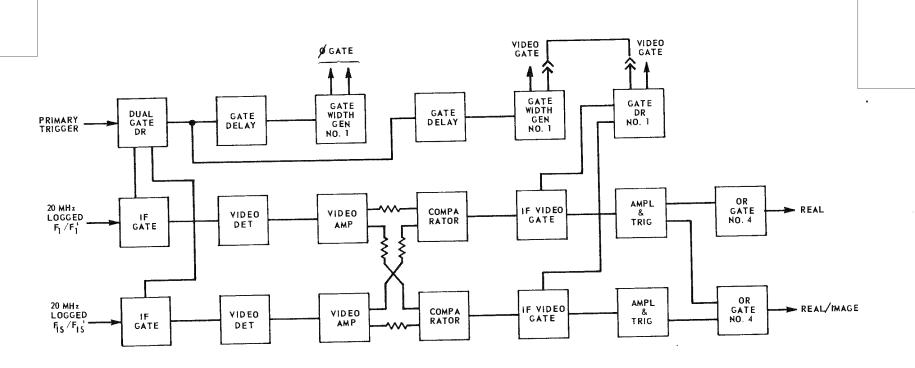

| 3.5-1                   | Real/Image Confirm Logic               | 75   |

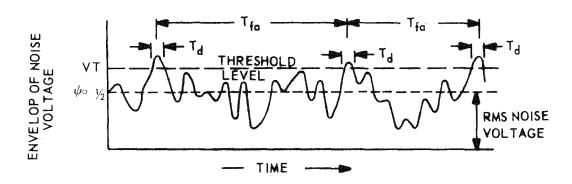

| 3.6-1                   | Average Noise Voltage Crossing vs Time | 81   |

| 3.7-1                   | Receiver Input vs Distance For Type A  |      |

|                         | Radar                                  |      |

| 3.7-2                   | Receiver Input vs Distance For Type B  |      |

|                         | Radar                                  |      |

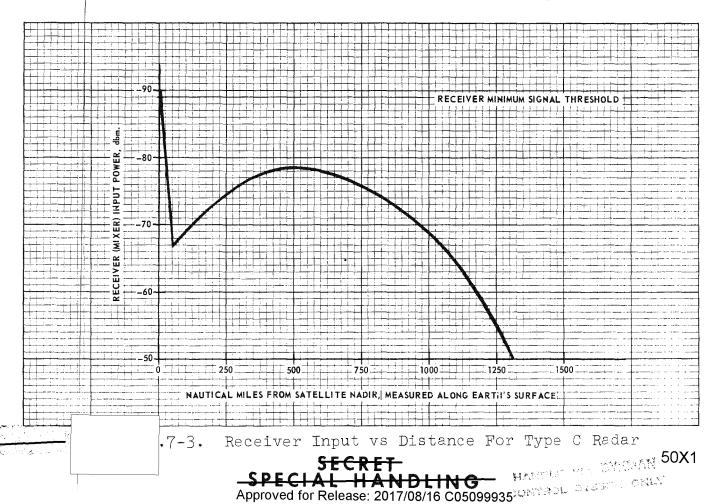

| 3 <b>.</b> 7 <b>-</b> 3 | Receiver Input vs Distance For Type C  |      |

|                         | Radar                                  |      |

Approved for Release: 2017/08/16 C05099935

### SPECIAL HANDLING

52000-R500 Page **xi**v

#### LIST OF FIGURES (Continued)

| Figure No. | <u>Title</u>                            | Page |

|------------|-----------------------------------------|------|

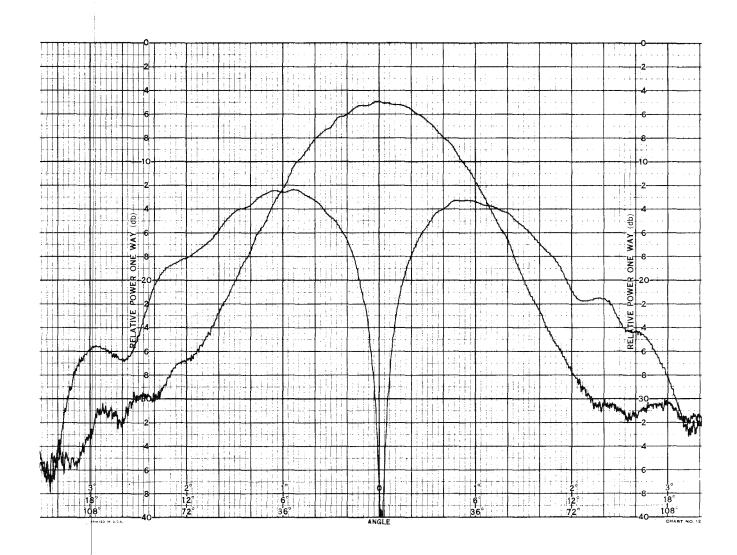

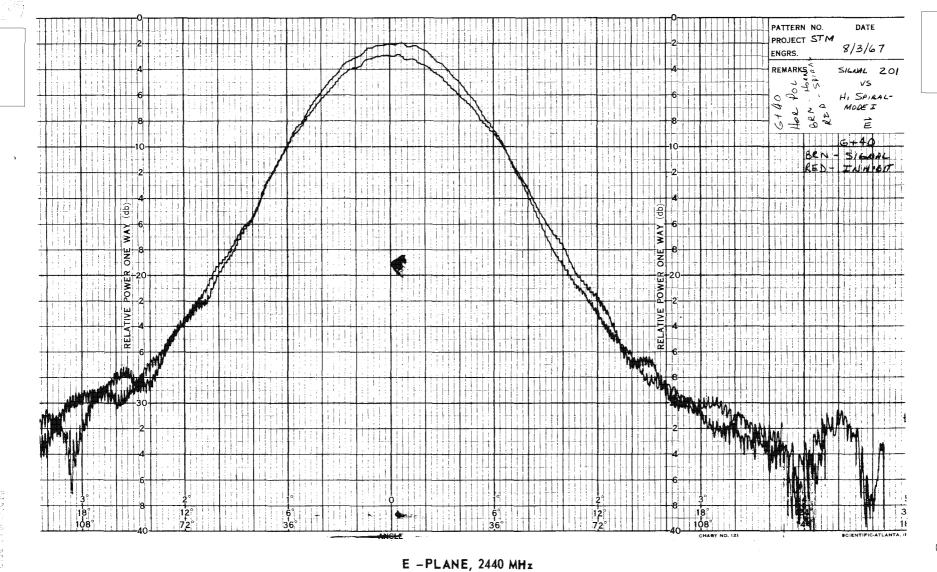

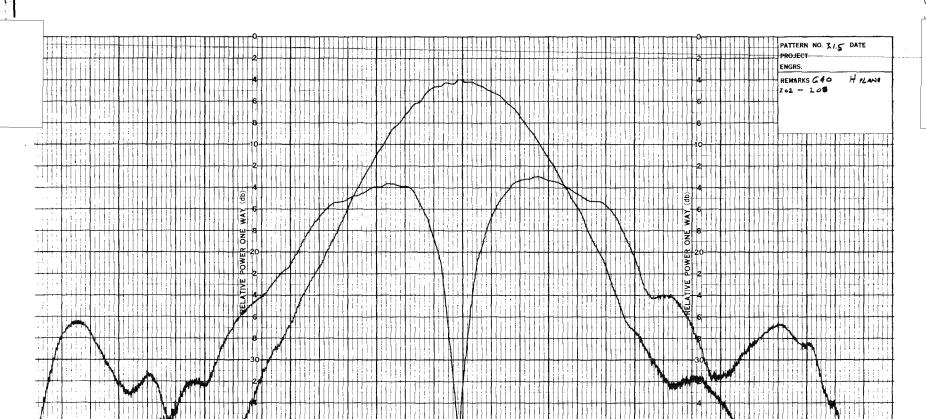

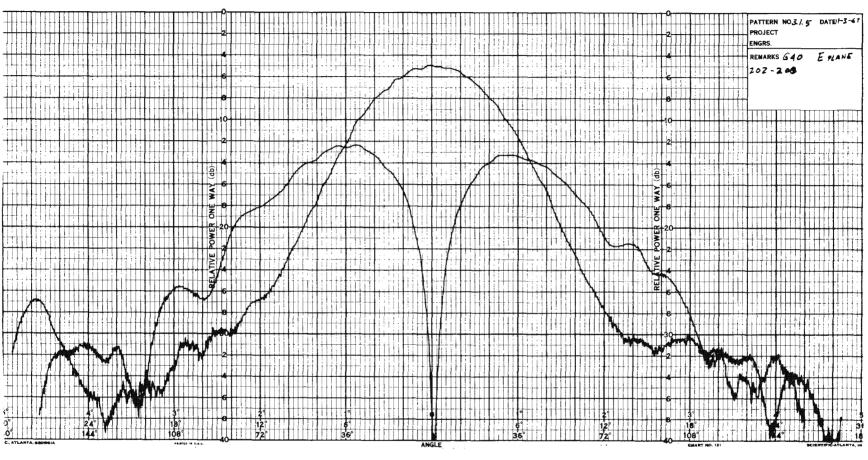

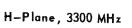

| 4 1-1      | E and H Plane Pattern of Phase Antennas | 103  |

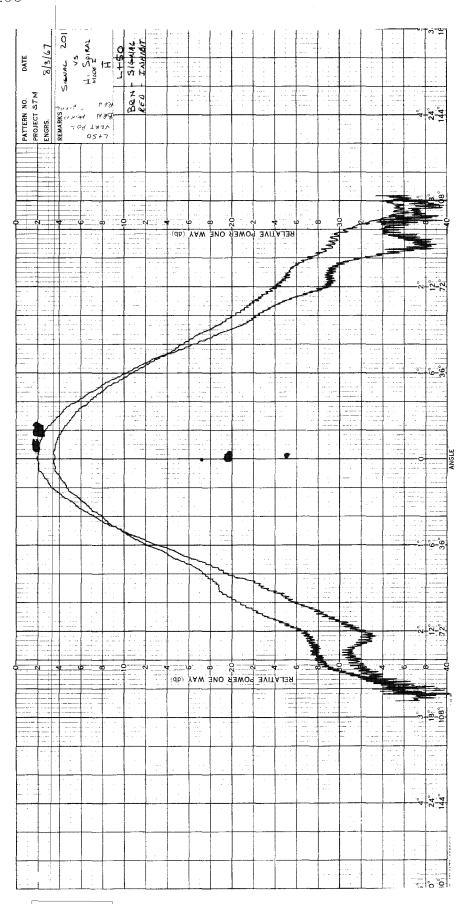

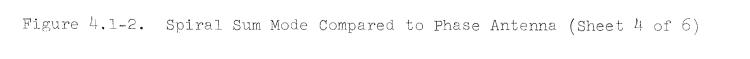

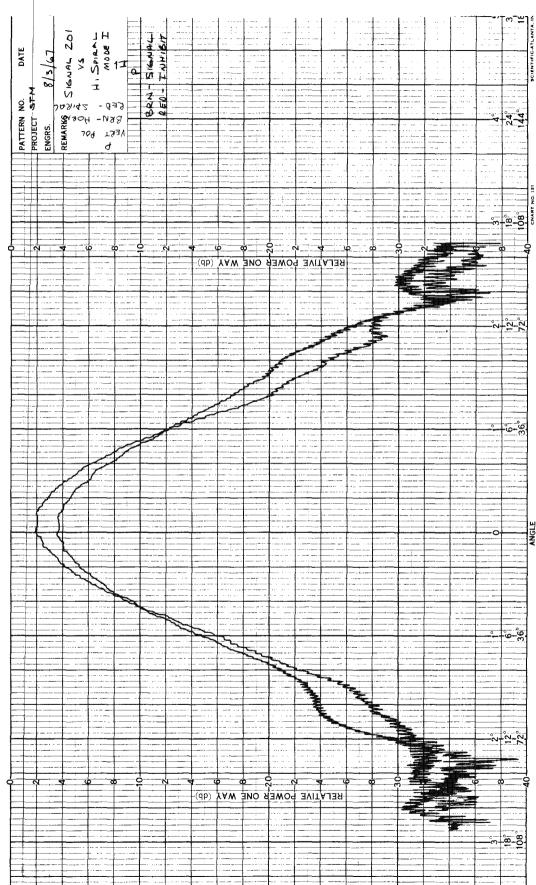

| 4.1-2      | Spiral Sum Mode Compared to Phase       |      |

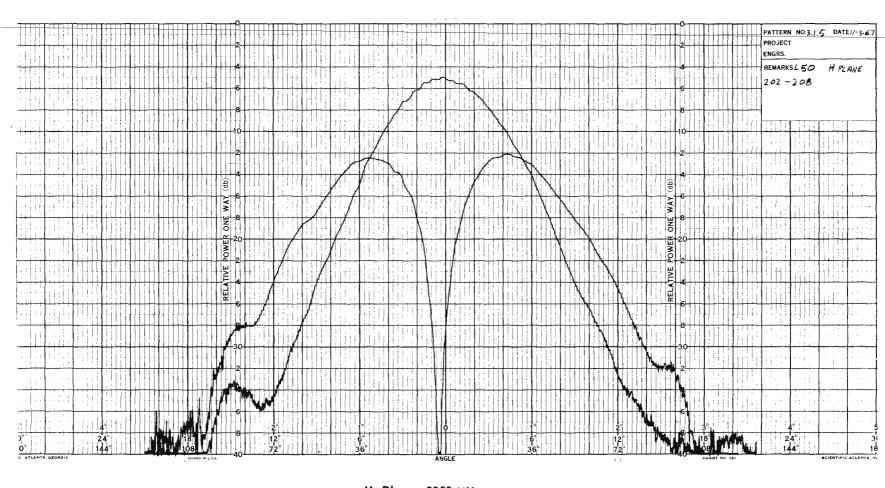

|            | Antenna                                 | 104  |

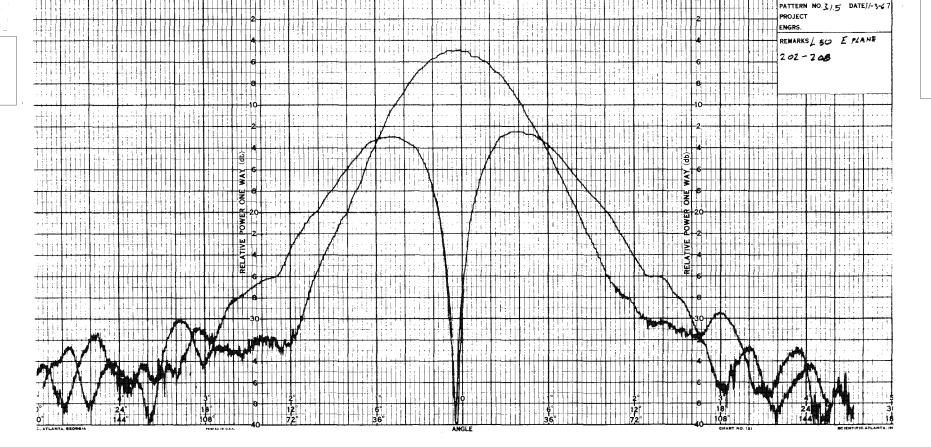

| 4.1-3      | Spiral Difference Mode Compared to      |      |

|            | Phase Antenna                           | 108  |

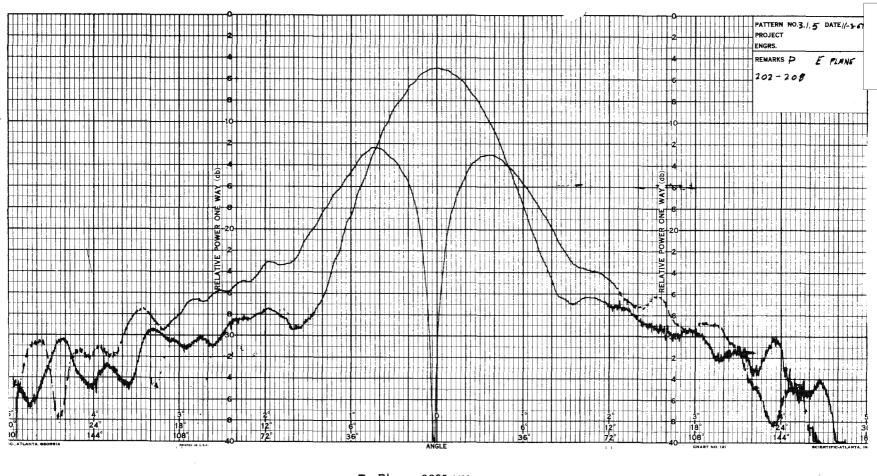

| 4 2-1      | RF Assembly Block Diagram               | 115  |

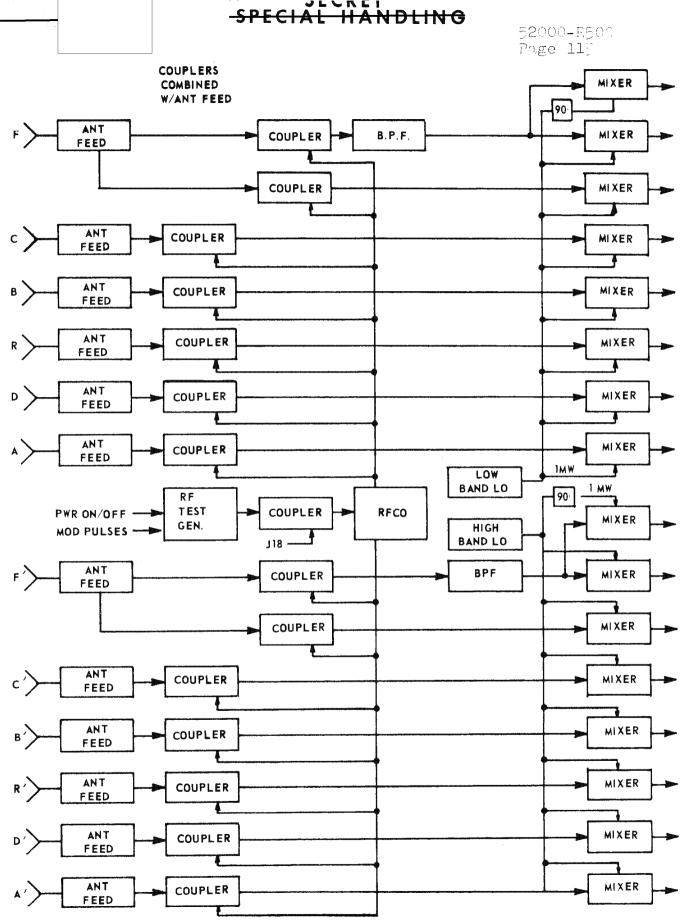

| 4.2-2      | RF Filter                               | 117  |

| 4 2-3      | Stripline Low Band Filter               | 118  |

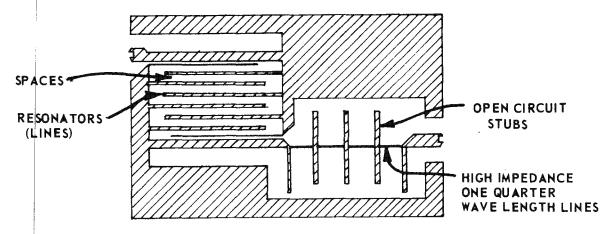

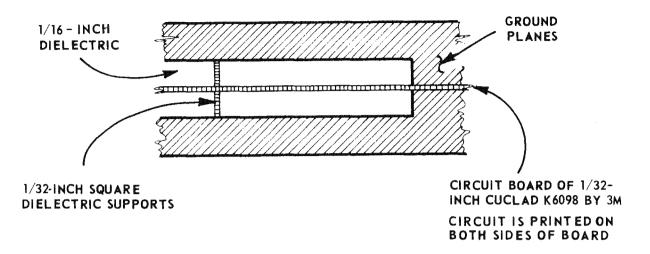

| 4.2.4      | Filter Construction                     | 119  |

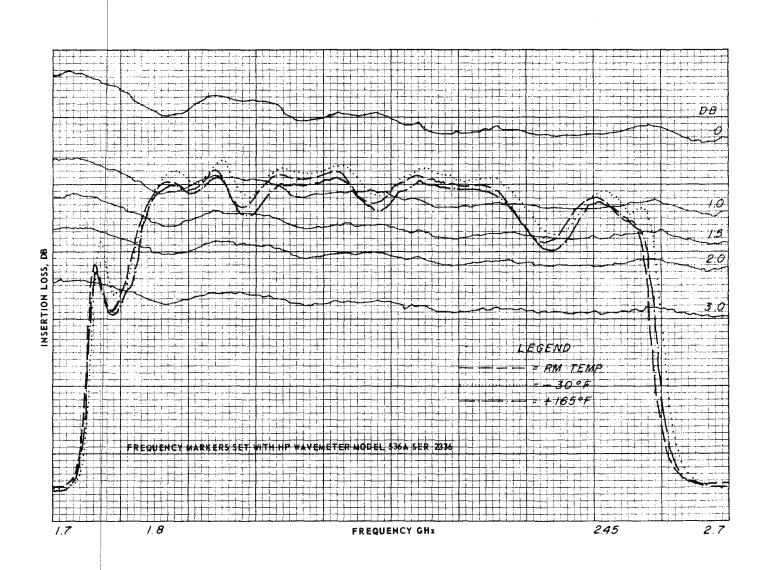

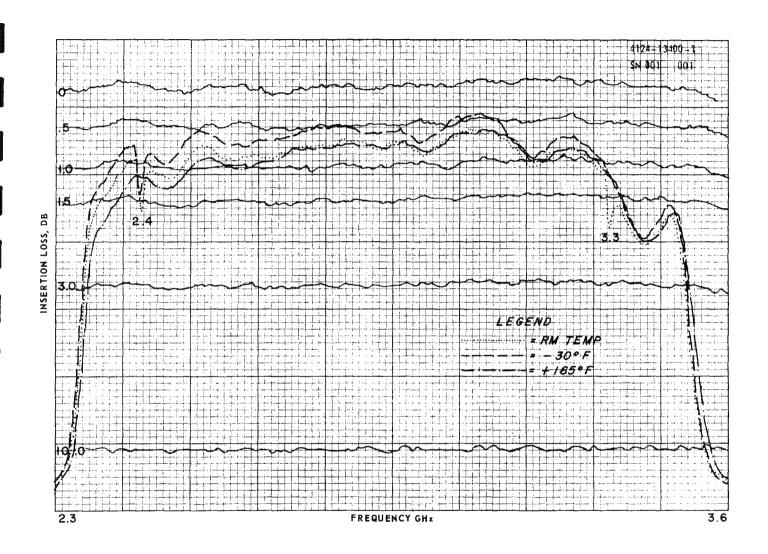

| 4.2-5      | Low Band Filter Functional Test         | 120  |

| 4.2-6      | High Band Filter Functional Test        | 121  |

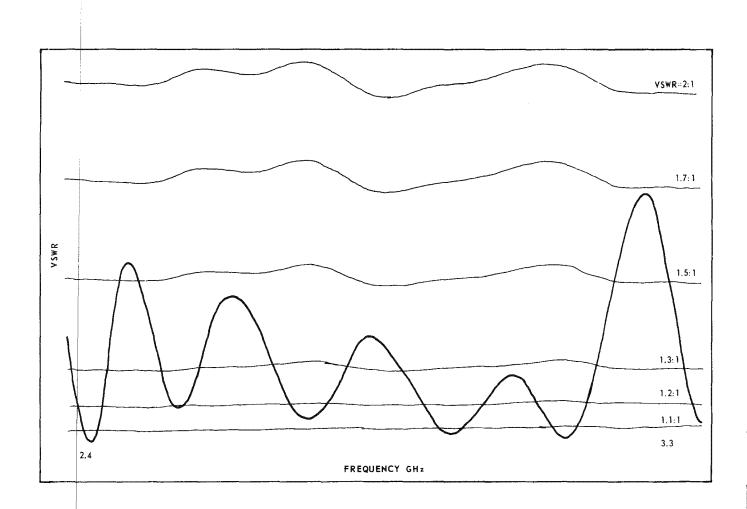

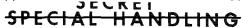

| 4.2-7      | High Band Filter VSWR                   | 122  |

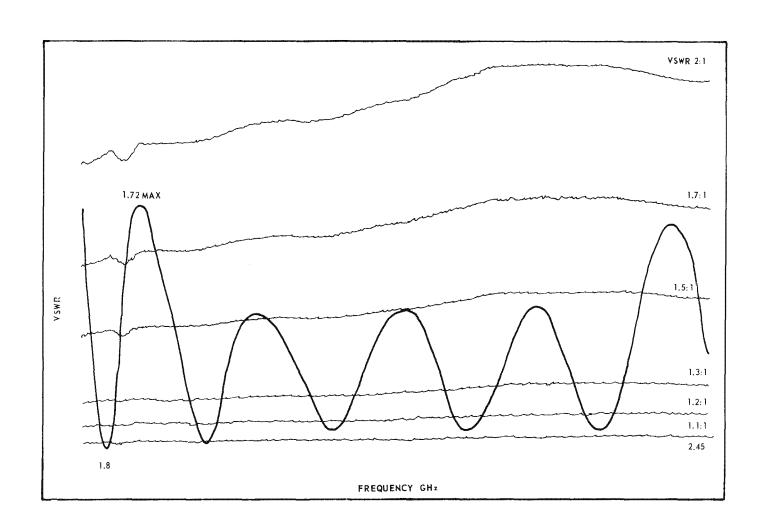

| 4.2-8      | Low Band Filter VSWR                    | 123  |

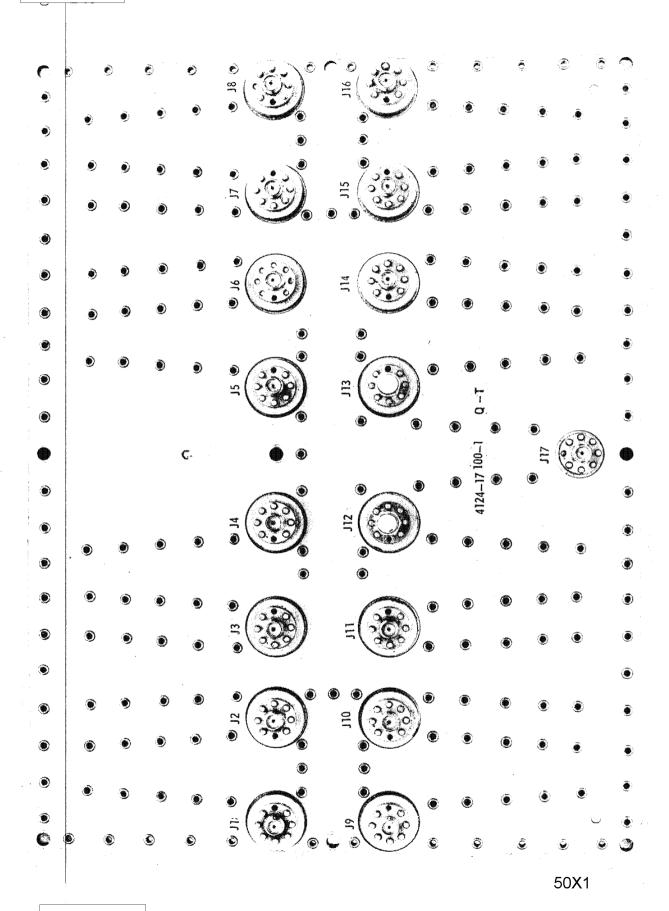

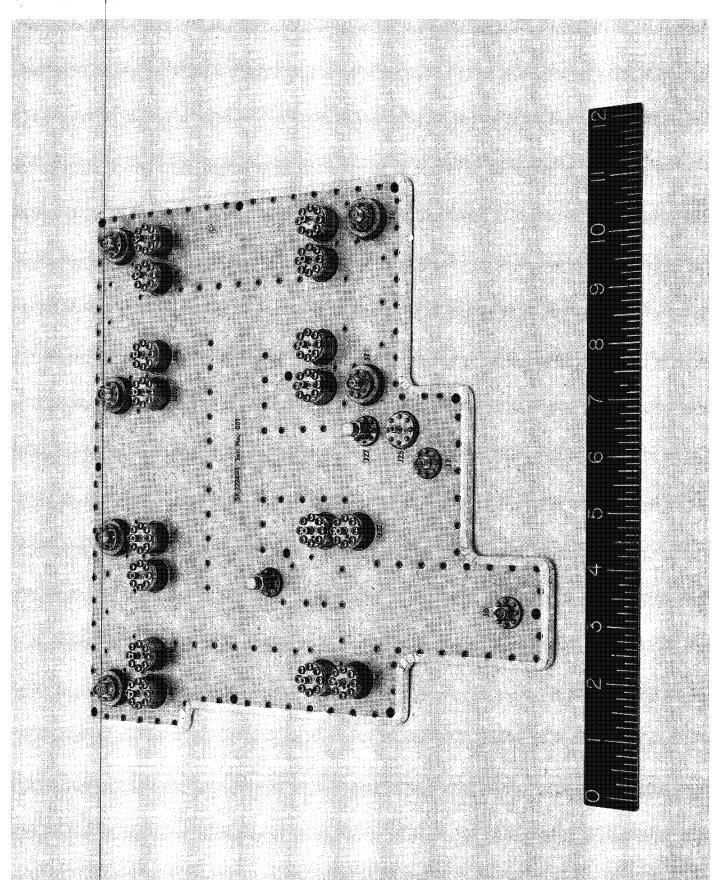

| 4.2-9      | RF Checkout Board                       | 126  |

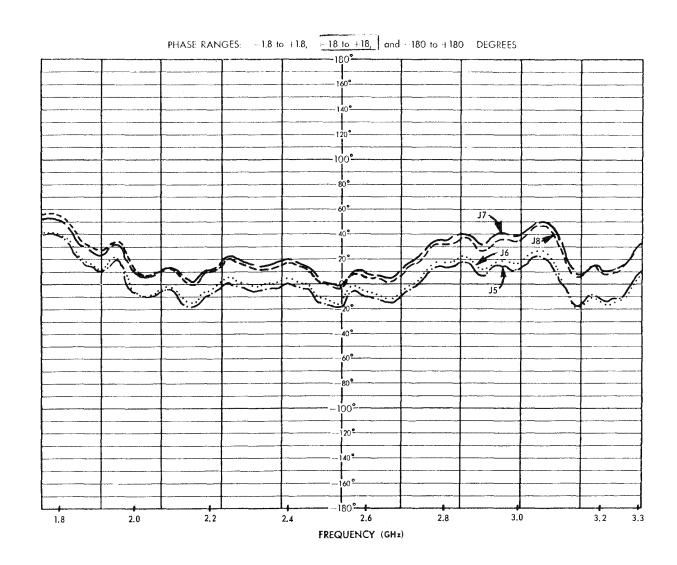

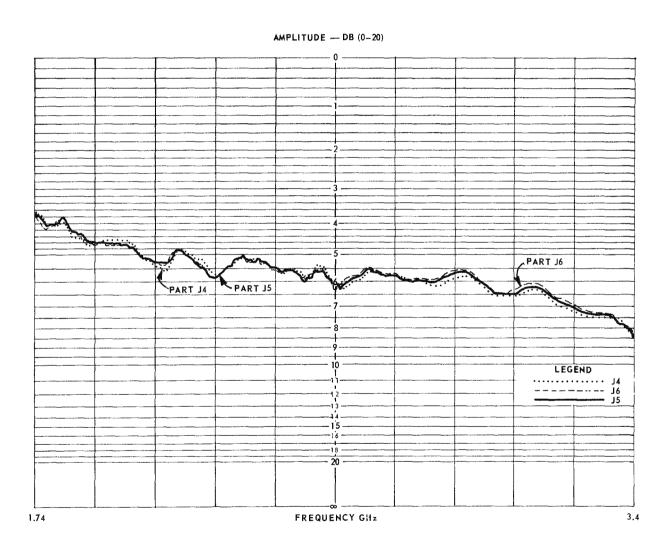

| 4.2-10     | RFC) Phase vs Frequency                 | 127  |

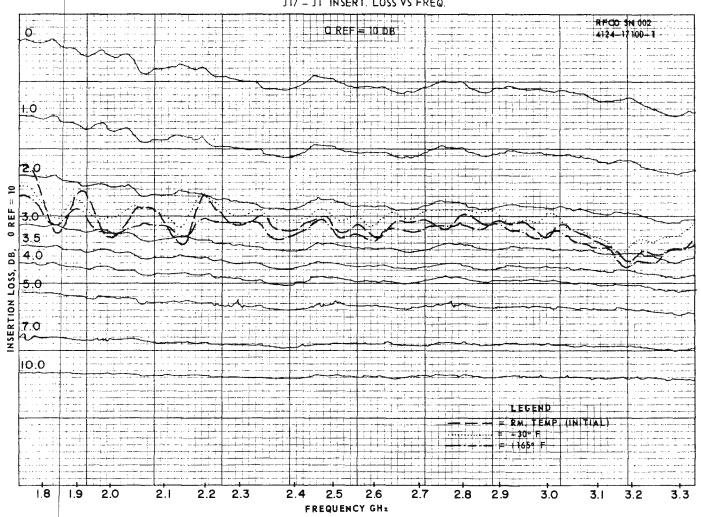

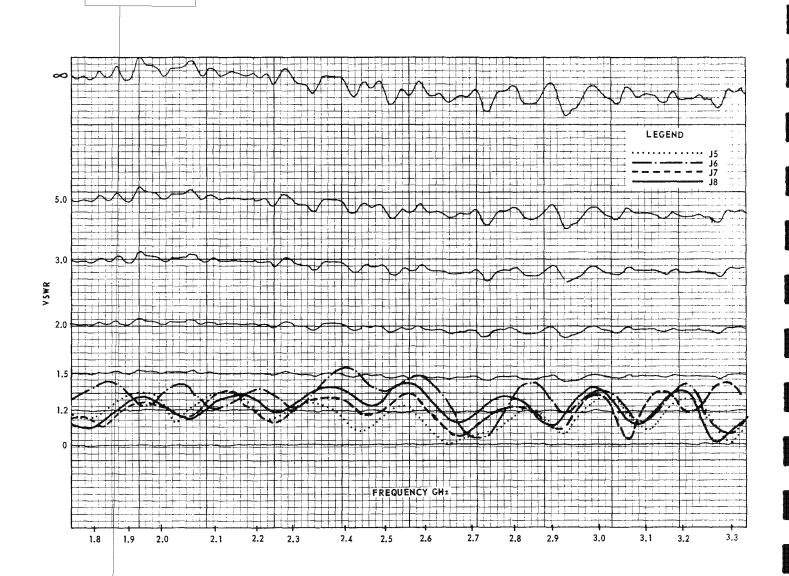

| 4.2-11     | J17-J1 Insertion Loss vs Frequency      | 128  |

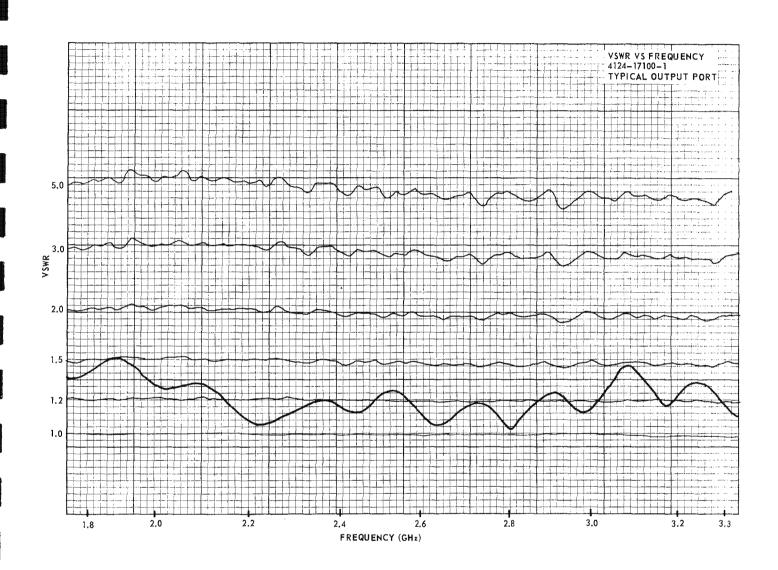

| 4.2-12     | Output VSWR vs Frequency                | 130  |

| 4.2-13     | Main Stripline                          | 132  |

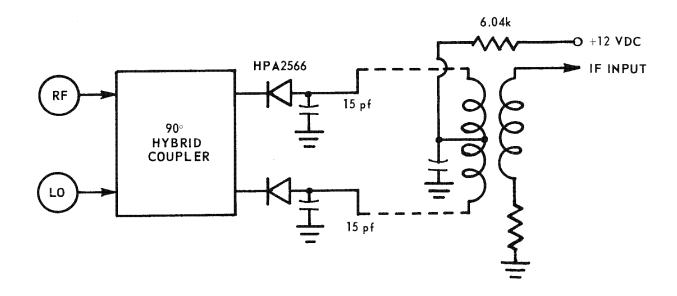

| 4.2-14     | Balanced Mixer                          | 133  |

| 4.2-15     | VSWR vs Frequency                       | 134  |

| 4.2-16     | Amplitude Variation With LO Frequency   | 135  |

| 4.2-17     | Boresight Phase                         | 136  |

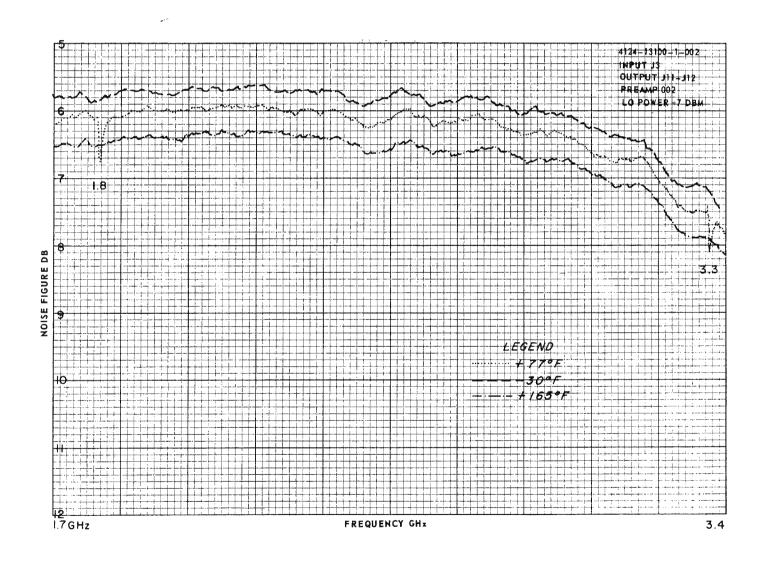

| 4.2-18     | Noise Figure vs Frequency               | 137  |

SPECIAL HANDLING

Approved for Release: 2017/08/16 C05099935

52000-R500 **Pa**ge xv

#### LIST OF FIGURES (Continued)

| Figure No. | <u>Title</u>                      | <u>Page</u> |

|------------|-----------------------------------|-------------|

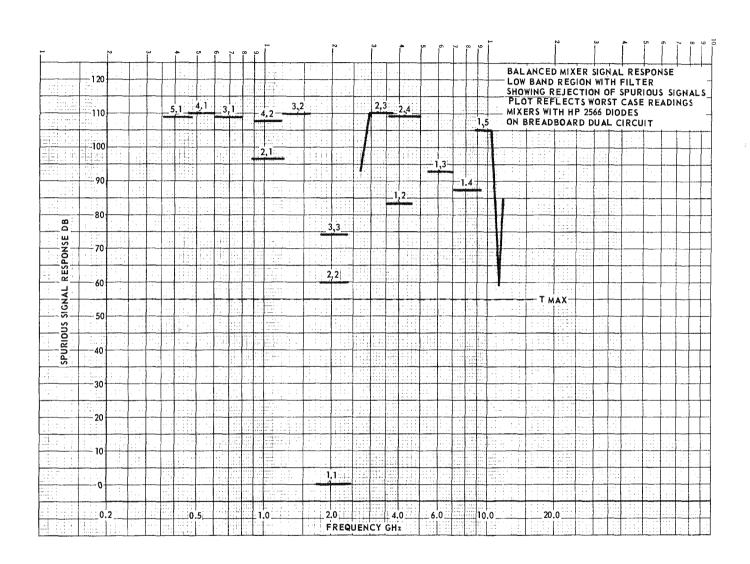

| 4.2-19     | Low Band Mixer Signal Response    | 139         |

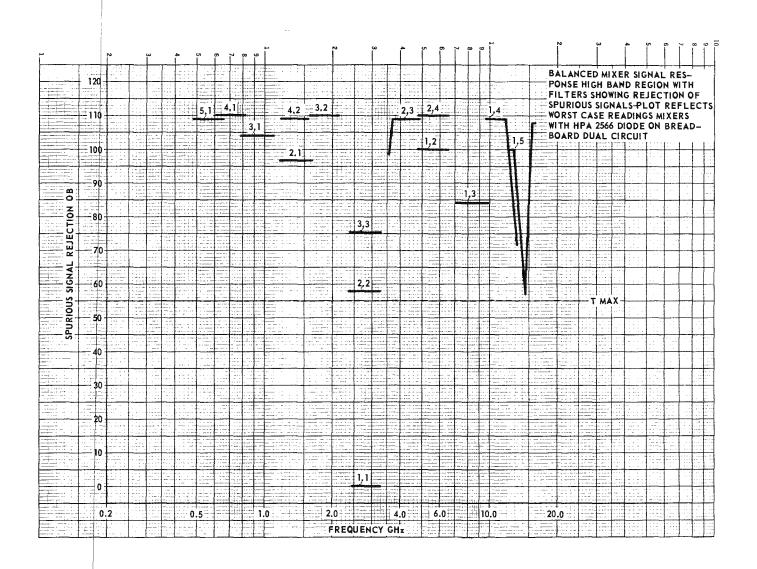

| 4.2-20     | High Band Mixer Signal Response   | 140         |

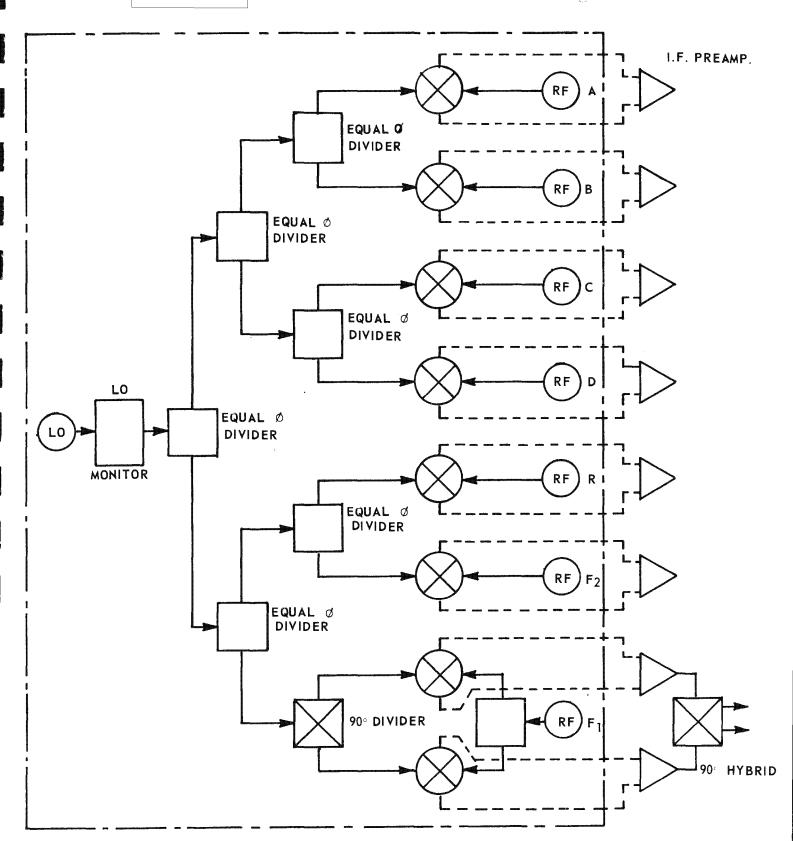

| 4.2-21     | Main Stripline Block Diagram      | 141         |

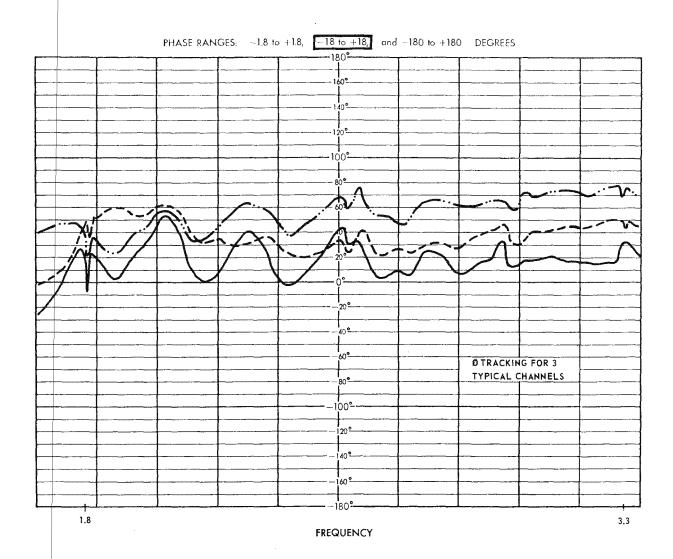

| 4.2-22     | Main Stripline Phase vs Frequency | 142         |

| 4.3-1      | LO Control Block Diagram          | 146         |

| 4.3-2      | Current Driver                    | 150         |

| 4.3-3      | Digital-To-Analog Converter       | 154         |

| 4.3-4      | Temperature Controller            | 158         |

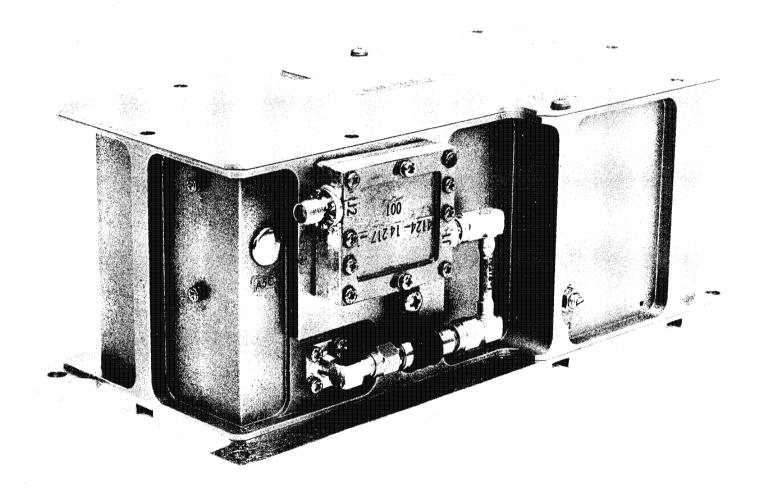

| 4.4-1      | RF Calibrator                     | 161         |

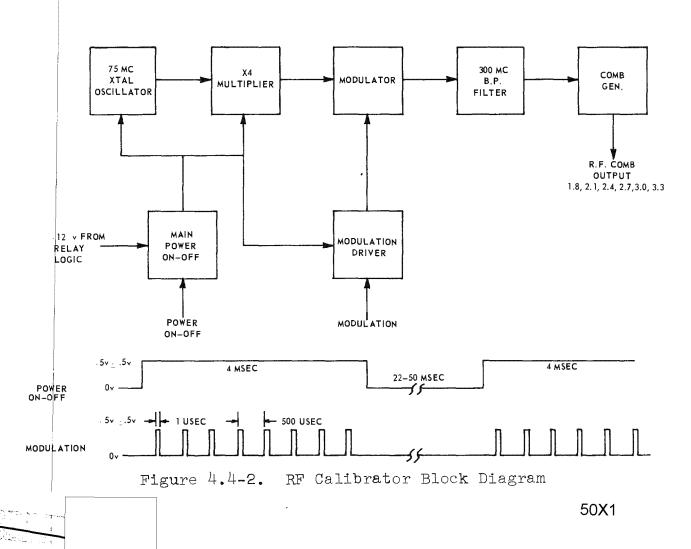

| 4.4-2      | RF Calibrator Block Diagram       | 162         |

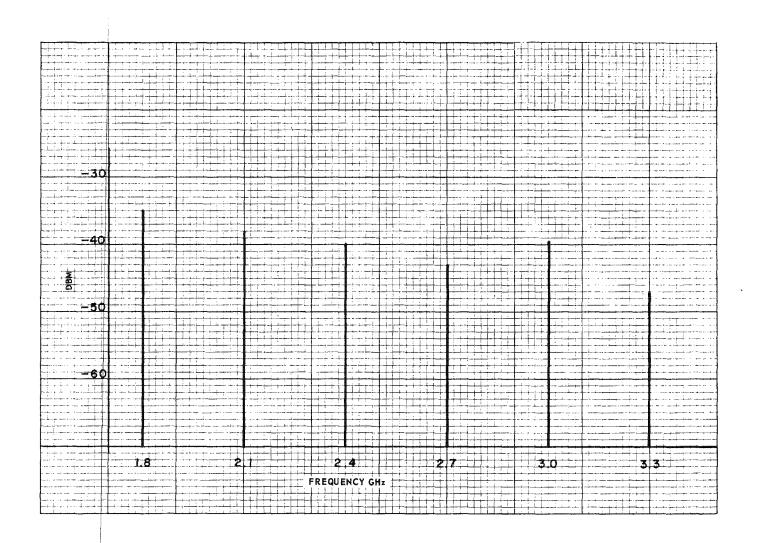

| 4.4-3      | Calibrator Frequency Spectrum     | 164         |

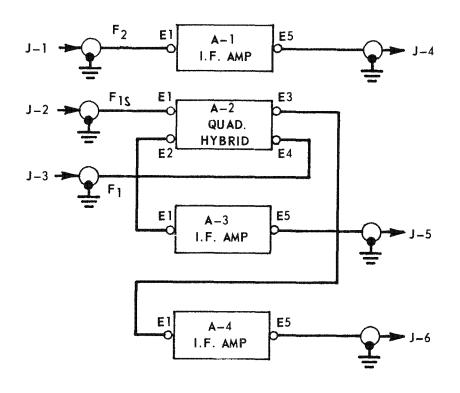

| 4.5-1      | IF Assembly Block Diagram         | 166         |

| 4.5-2      | Hybrid                            | 175         |

| 4.5-3      | Typical IF Phase Channel          | 180         |

| 4.5-4      | IF Phase Channel C                | 181         |

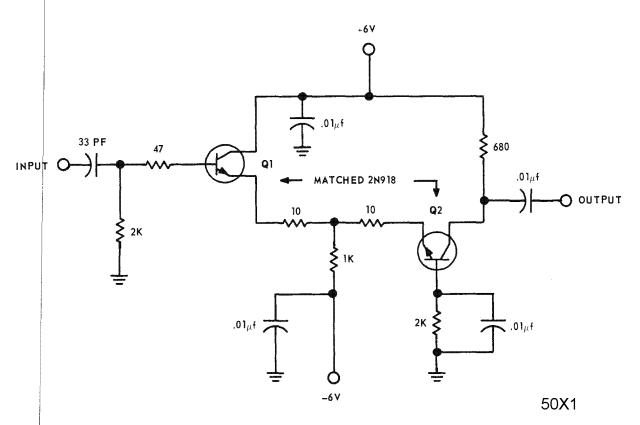

| 4.5-5      | First Limiter                     | 184         |

| 4.5-6      | Phase Detector                    | 190         |

| 4.5-7      | Phase Detector Timing             | 191         |

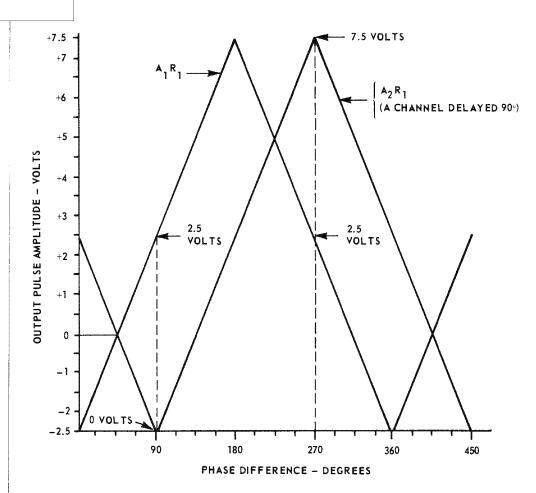

| 4.5-8      | Phase Detector Response Curve     | 192         |

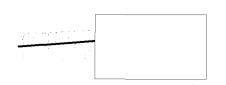

| 4.5-9      | Frequency Confirm                 | 199         |

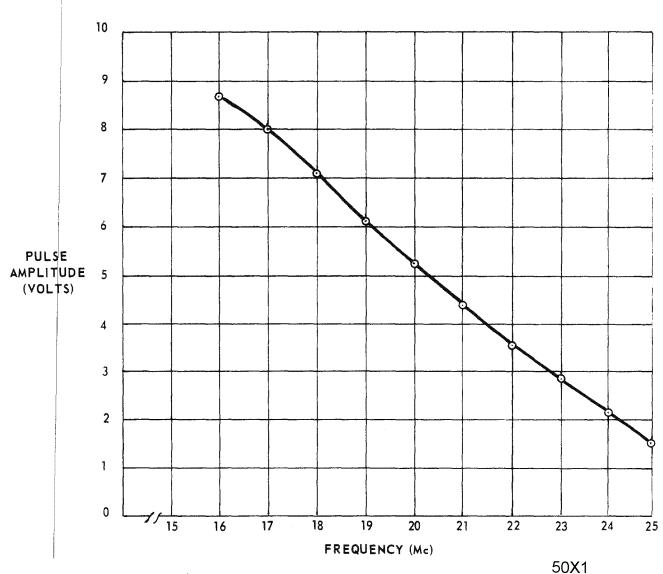

| 4.5-10     | Pulse Amplitude vs Frequency      | 200         |

| 4.5-11     | Log IF Block Diagram              | 204         |

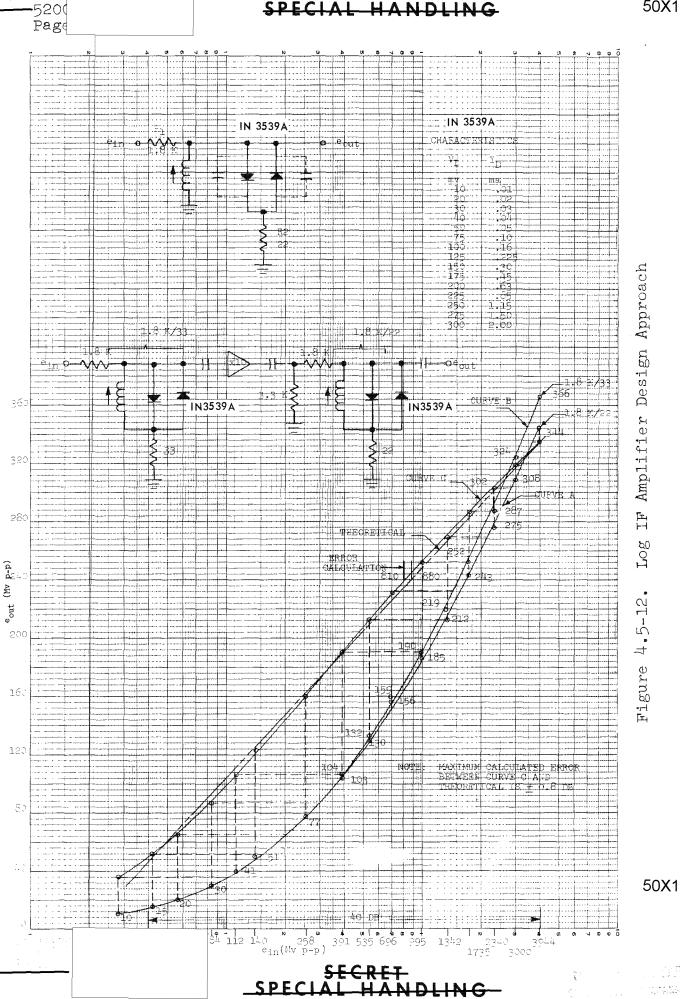

| 4.5-12     | Log IF Amplifier Design Approach  | 206         |

PANOLE VIN BYEIGH Coathain on that, and the

#### SPECIAL HANDLING

52000-R500 Page xvi

#### LIST OF FIGURES (Continued)

| Figure No. | <u>Title</u>                         | <u>Page</u> |

|------------|--------------------------------------|-------------|

| 4.5-13     | Log IF Amplifier Characteristics     | 209         |

| 4.5-14     | Signal-Indicate Generator            | 213         |

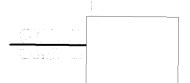

| 4.5-15     | A/R and P-W Confirm Block Diagram    | 220         |

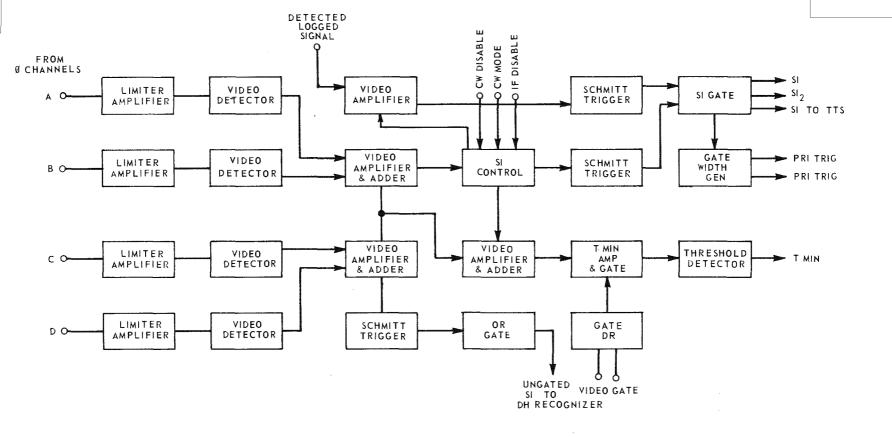

| 4.5-16     | Real-Image Logic Block Diagram       | 230         |

| 4.5-17     | TTS Converter Block Diagram          | 238         |

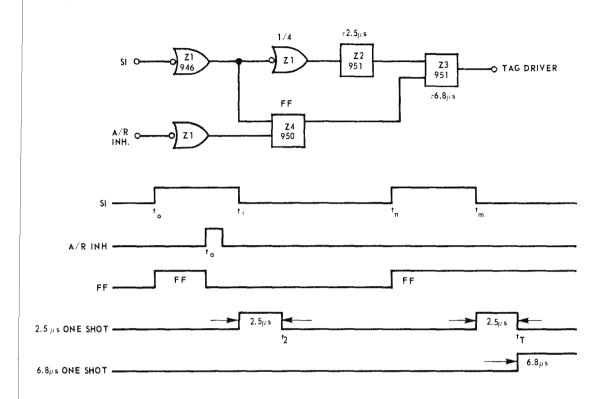

| 4.5-18     | Tag Pulse                            | 242         |

| 4.5-19     | Tag Logic                            | 244         |

| 4 5-20     | Recognizer Amplitude Threshold       |             |

|            | Block Diagram                        | 248         |

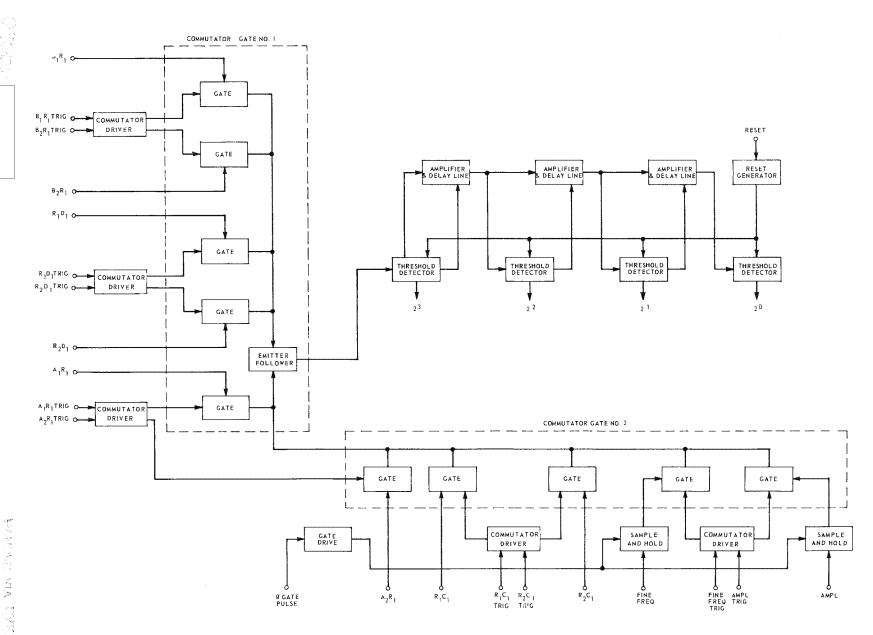

| 4 5-21     | Analog-to-Digital Converter          | 251         |

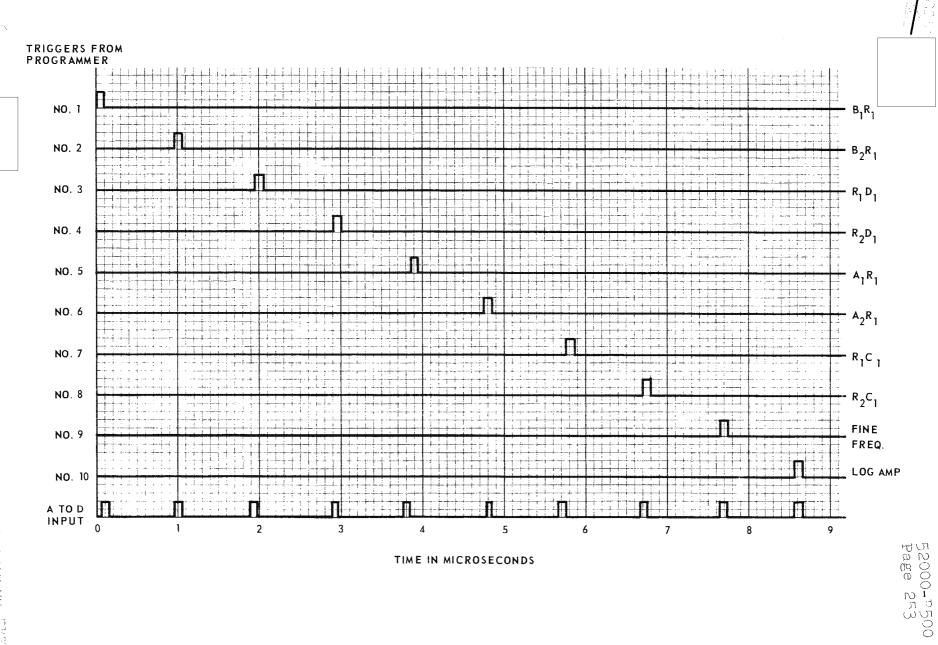

| 4 5-22     | Commutator Timing Diagram            | 253         |

| 4 5-23     | Analog-to-Digital Timing Diagram     | 257         |

| 4.6-1      | Phase Combiner Block Diagram         | 266         |

| 4,6-2      | Phase Combiner Timing Diagram        | 267         |

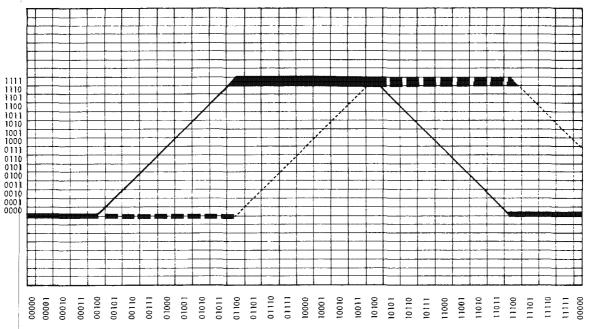

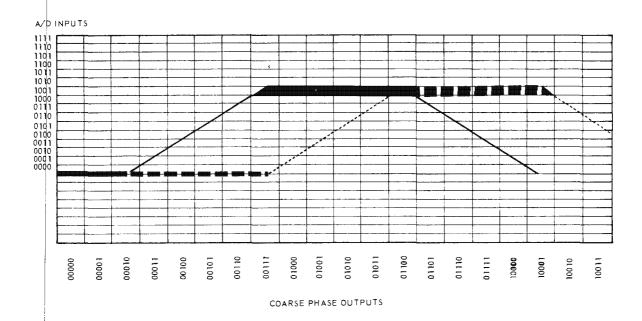

| 4.6-3      | Phase Combiner Outputs               | 268         |

| 4,6-4      | Phase Coder Block Diagram            | 275         |

| 4.6-5      | System Field of View                 | 277         |

| 4.6-6      | Buffer Storage Logic Block Diagram   | 282         |

| 4.6-7      | Buffer Storage Overall Block Diagram | 284         |

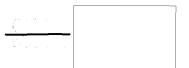

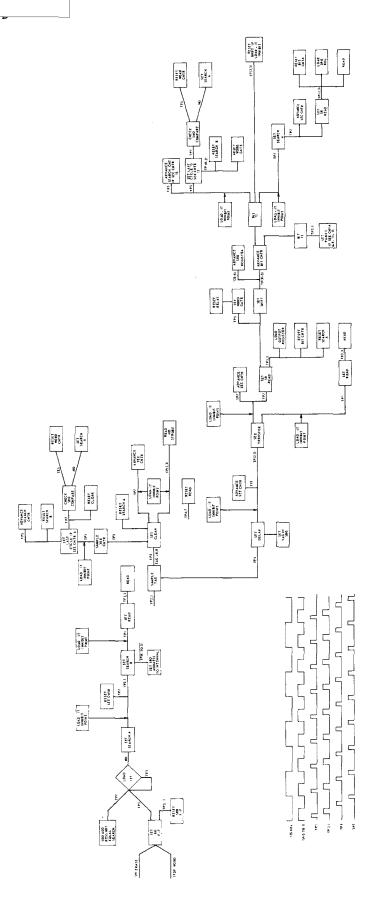

| 4.6-8      | Load Routine Flow Chart              | 287         |

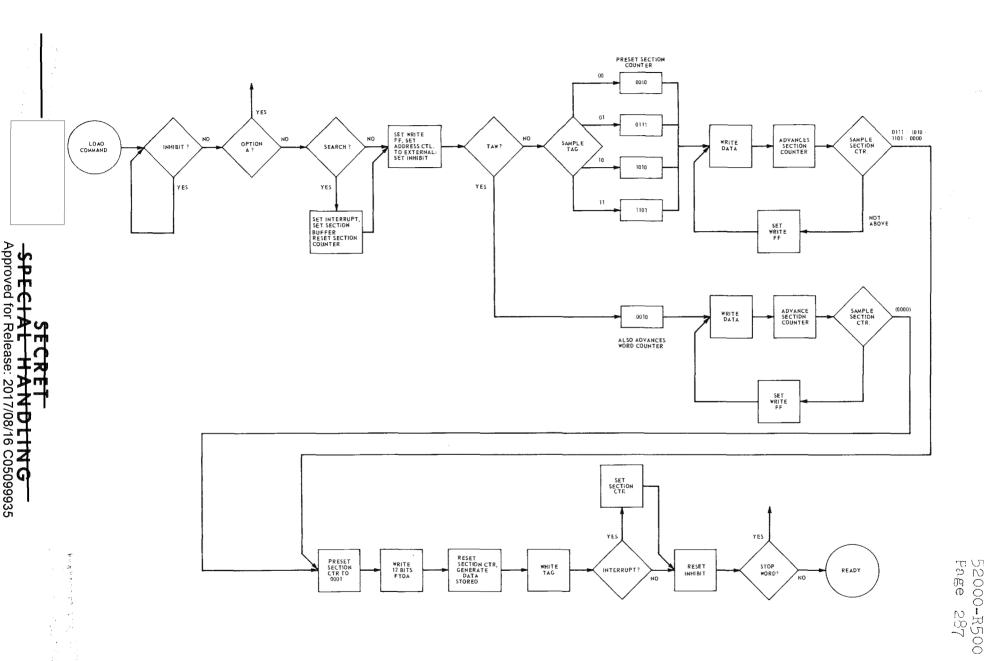

| 4.6-9      | Load Routine Timing                  | 288         |

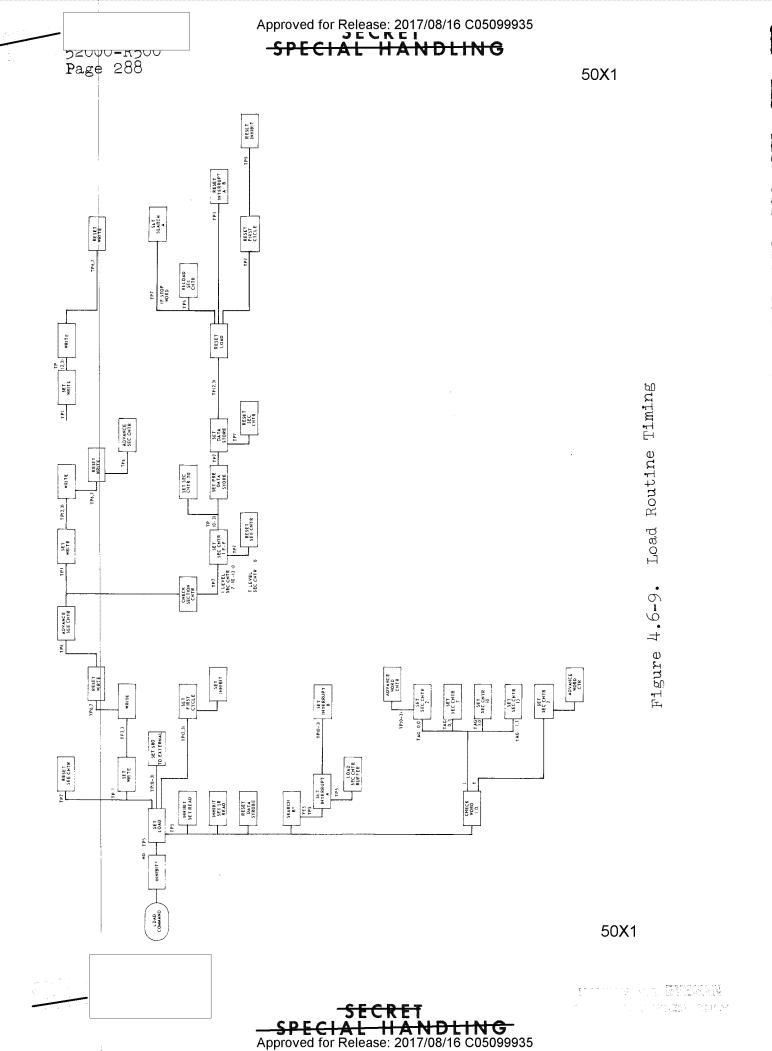

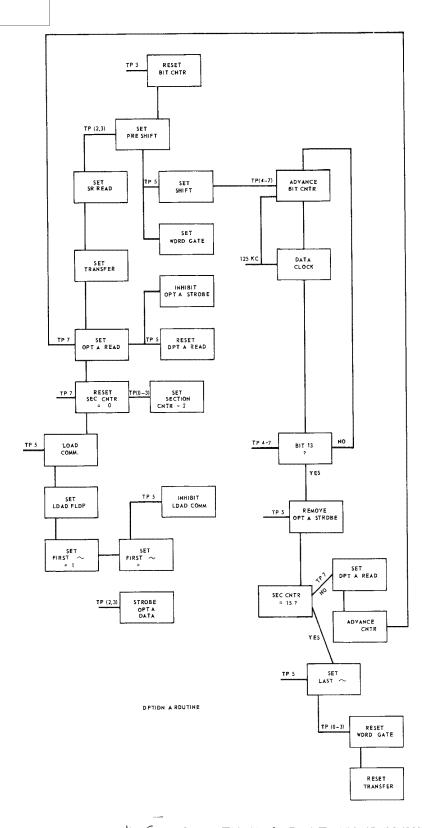

| 4.6-10     | Option A Flow Chart                  | 289         |

| 4.6-11     | Option A Routine Timing              | 290         |

Ten ende var **en** andelf f

52000-R500 Page xvii

#### LIST OF FIGURES (Continued)

| Figure No.      | <u>Title</u>                       | <u>Page</u> |

|-----------------|------------------------------------|-------------|

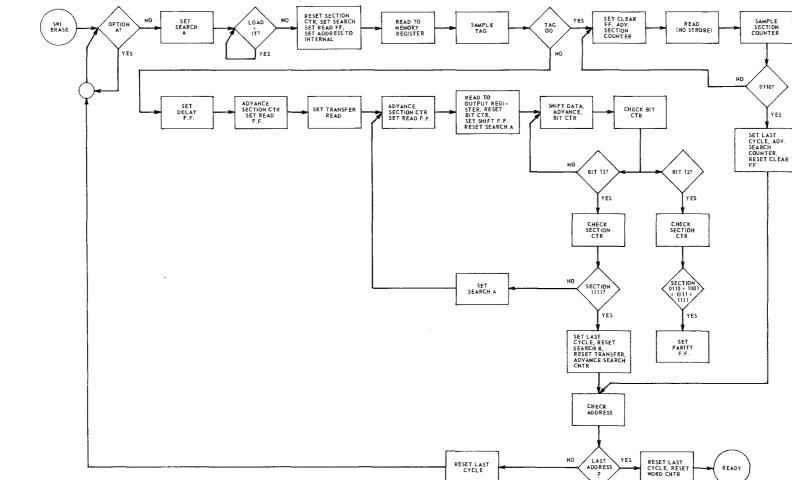

| 4.6-12          | Output Routine Flow Chart          | 291         |

| 4.6-13          | Output Routine Timing              | 292         |

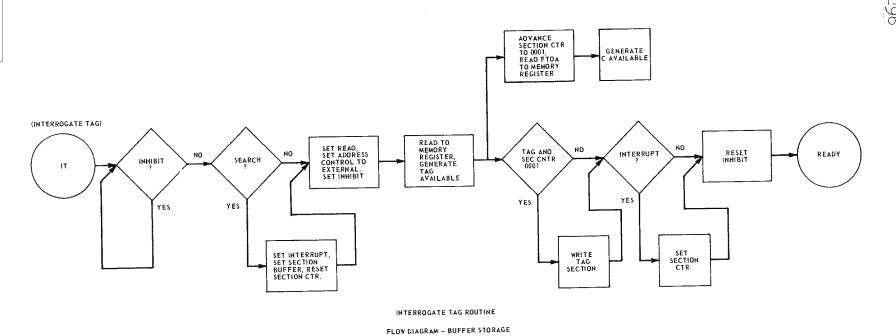

| 4.6-14          | Interrogate Tag Routine Flow Chart | 296         |

| 4.6-15          | Interrogate Tag Routine Timing     | 297         |

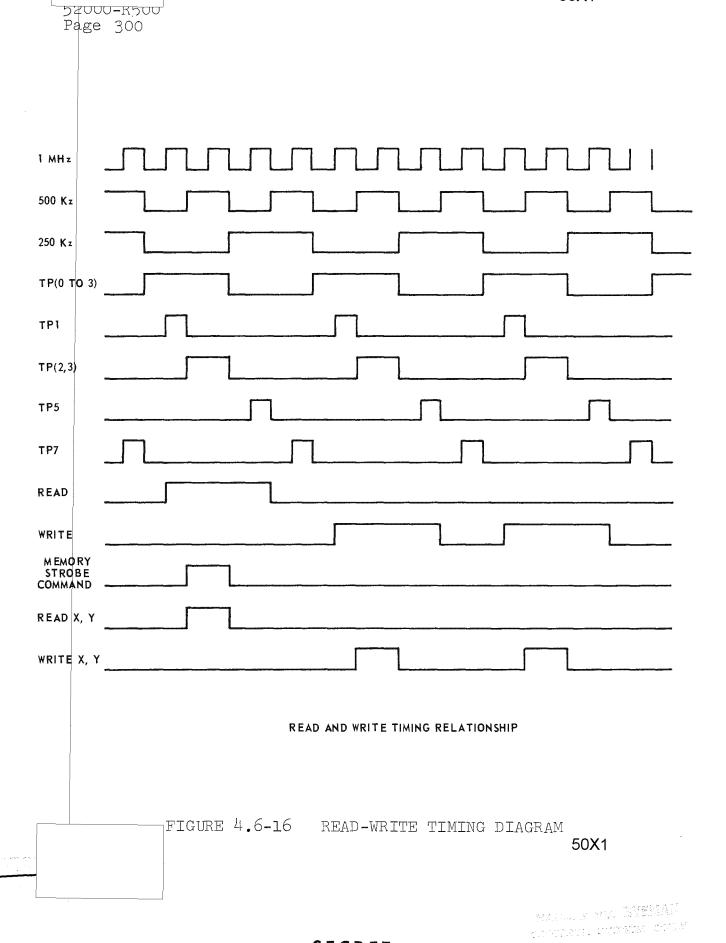

| 4.6-16          | Read-Write Timing Diagram          | 300         |

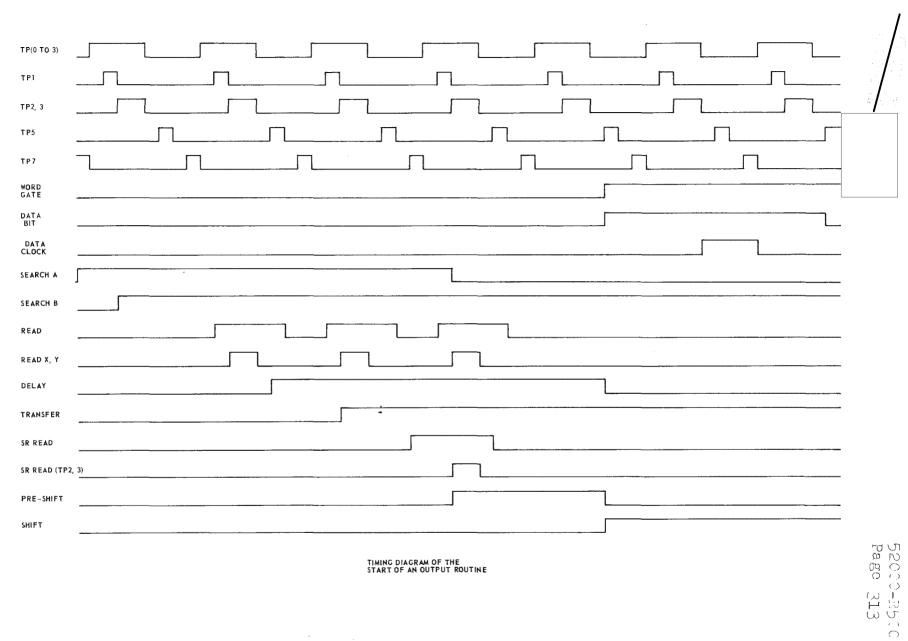

| 4.6-17          | Timing of Start of Output Routine  | 313         |

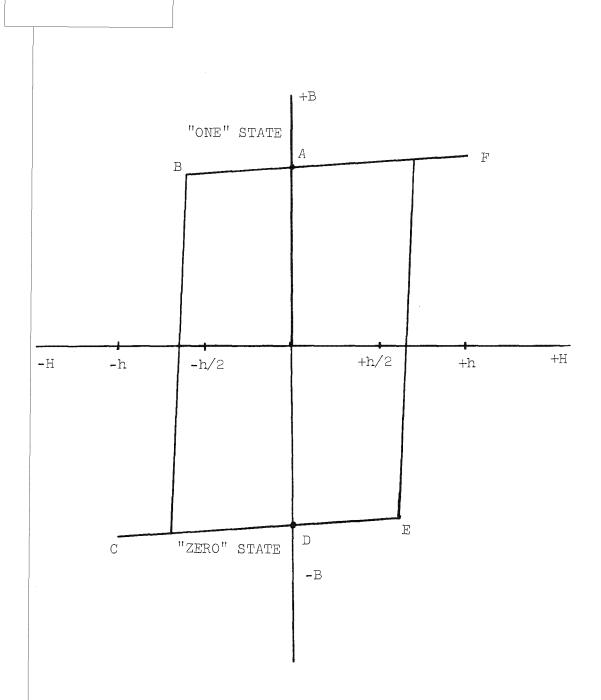

| 4.6-18          | Hysteris Loop                      | 318         |

| 4.6-19          | Core Array                         | 321         |

| 4.6-20          | Driver/Sink Technique              | 324         |

| 4.6-21          | Selection Current Timing           | 330         |

| 4.6-22          | SWI Block Diagram                  | 332         |

| 4.6-23          | Buffer Storage Memory              | 334         |

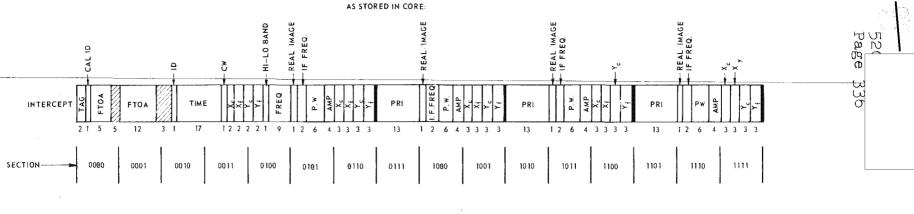

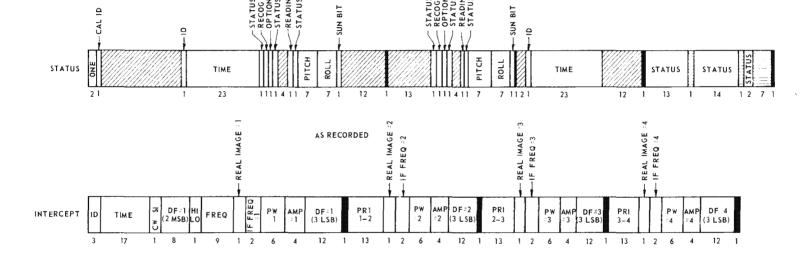

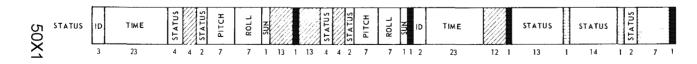

| 4.6-24          | Data Word Format                   | 336         |

| 4.6-25          | Recognizer Memory                  | 338         |

| 4 <b>.6-</b> 26 | System Clock                       | 340         |

| 4.6-27          | Pulse Width Encoder                | 344         |

| 4.6-28          | Attitude Encoder                   | 351         |

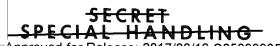

| 4.6-29          | Ramp Generator                     | 353         |

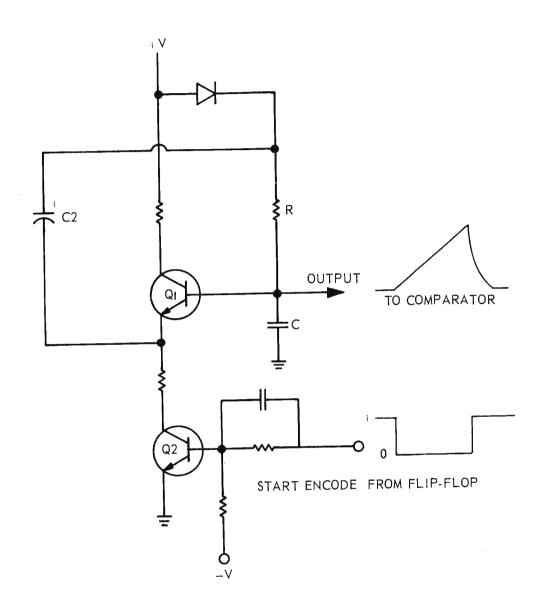

| 4.6-30          | Voltage Comparator                 | 354         |

| 4.6-31          | Calibrate Signal Generator, Block  |             |

|                 | Diagram                            | 357         |

| 4.6-32          | Calibrate Signal Generator, Timing |             |

|                 | Diagram                            | 358         |

PARKELS AN BARRAN e where bytelin orly

# Approved for Release: 2017/08/16 C05099935 SPECIAL HANDLING

52000-R500 Page xviii

#### LIST OF FIGURES (Continued)

| Figure No. | <u>Title</u>                        | Page       |

|------------|-------------------------------------|------------|

| 4.6-33     | Marker Word Generator               | 368        |

| 4.6-34     | Scan Control Block Diagram          | 375        |

| 4.6-35     | Scan Control Timing Diagram         | 379        |

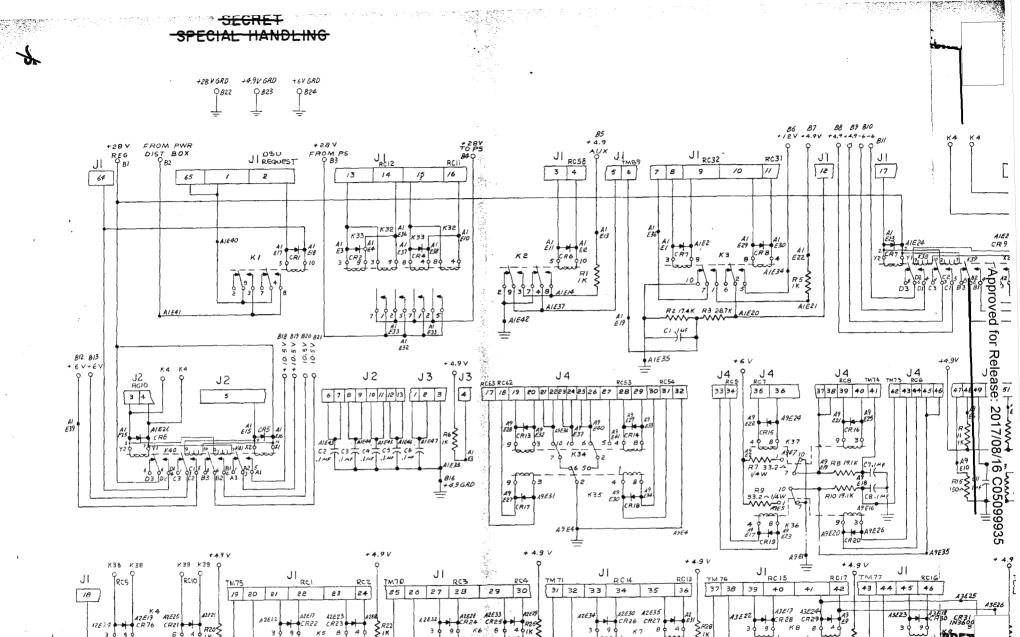

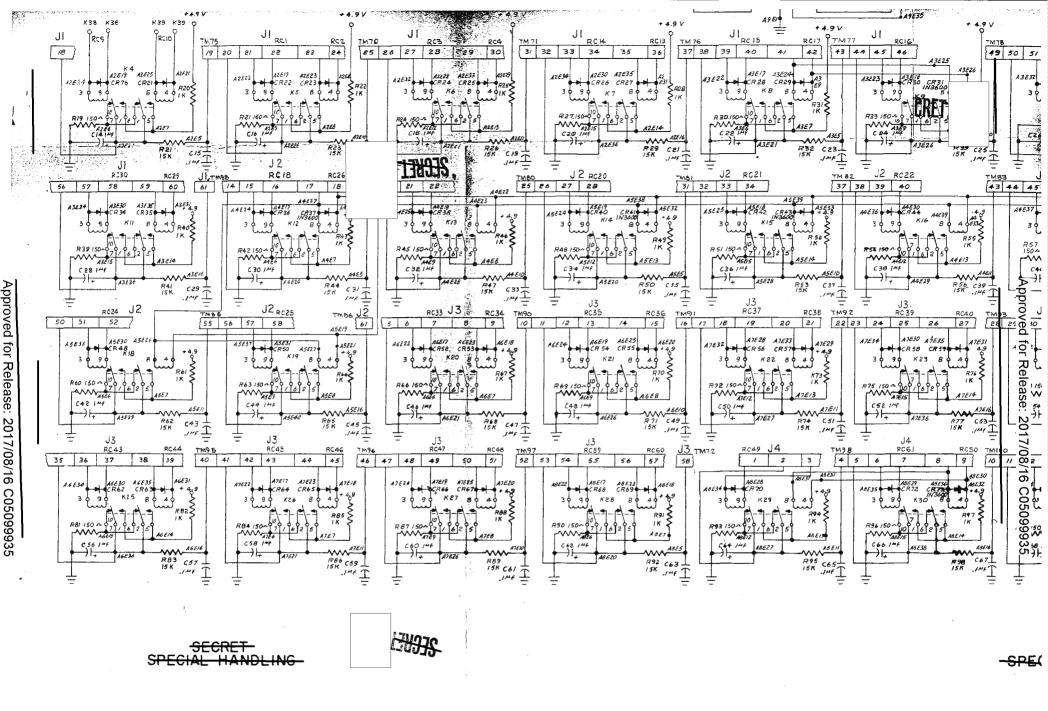

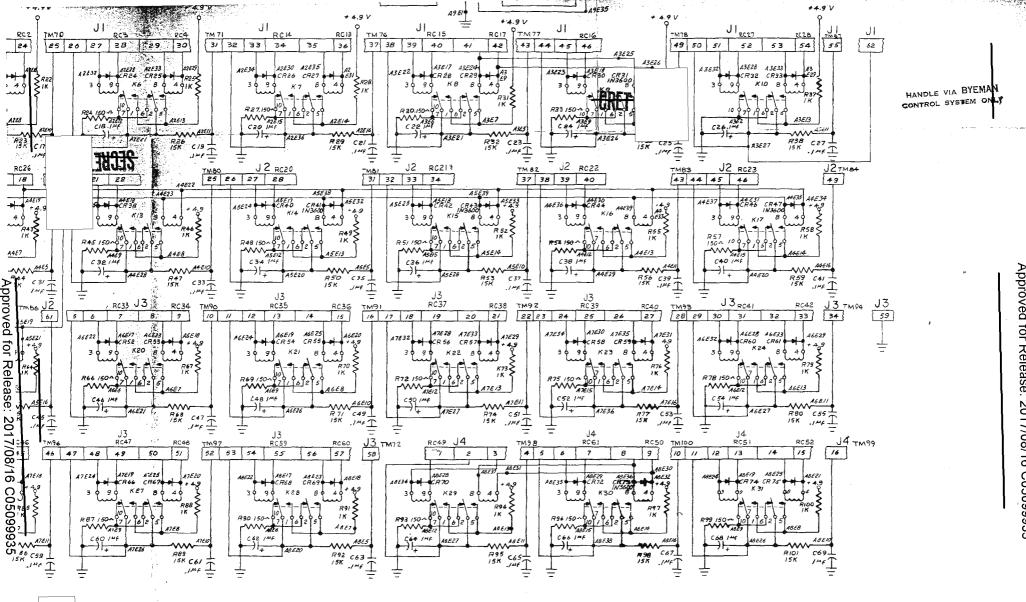

| 4.6-36     | Relay Assembly Schematic Diagram    | 385<br>386 |

| 4.6-37     | Inverting Operational Amplifier     | 396        |

| 4.6-38     | Operational Amplifier Response      | 397        |

| 4.6-39     | Typical F.E.T. Circuit              | 399        |

| 4.6-40     | F.E.T. Response                     | 400        |

| 4.6-41     | Non-Inverting Operational Amplifier | 401        |

| 4,6-42     | Non-Inverting Response              | 402        |

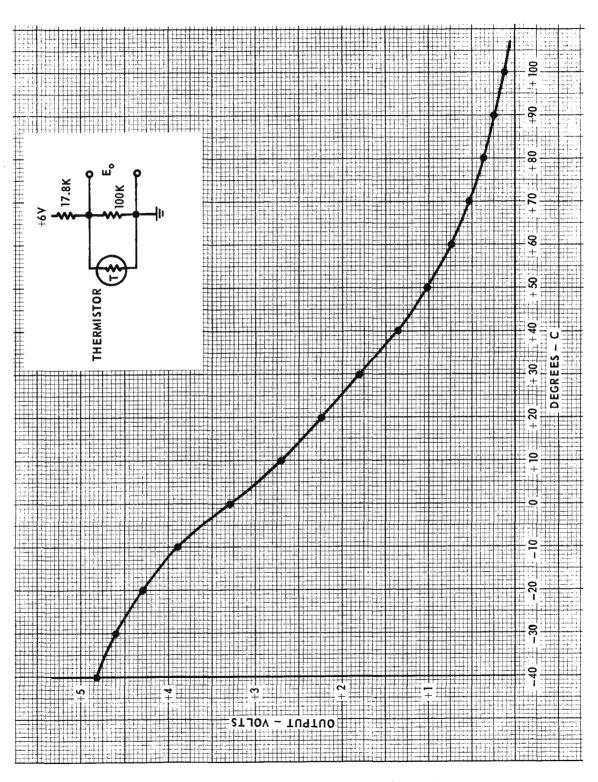

| 4.6-43     | Typical Thermistor Response         | 403        |

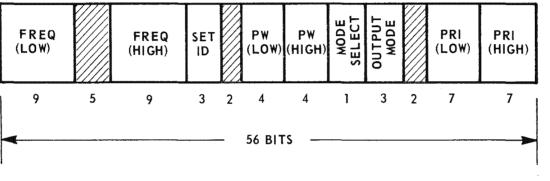

| 4.7-1      | Subword Format                      | 409        |

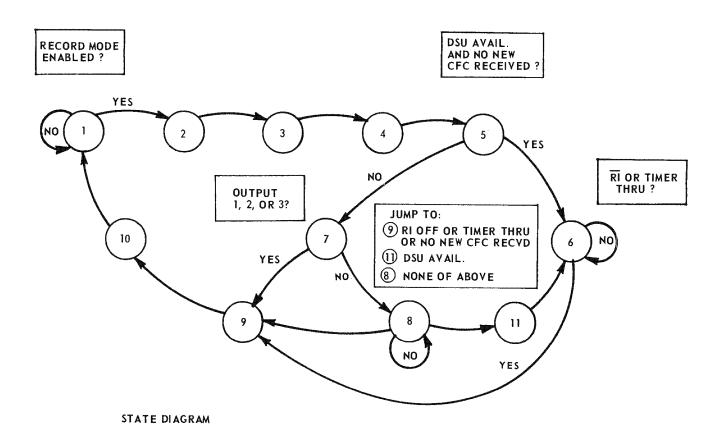

| 4.7-2      | Frequency Mode State Diagram        | 427        |

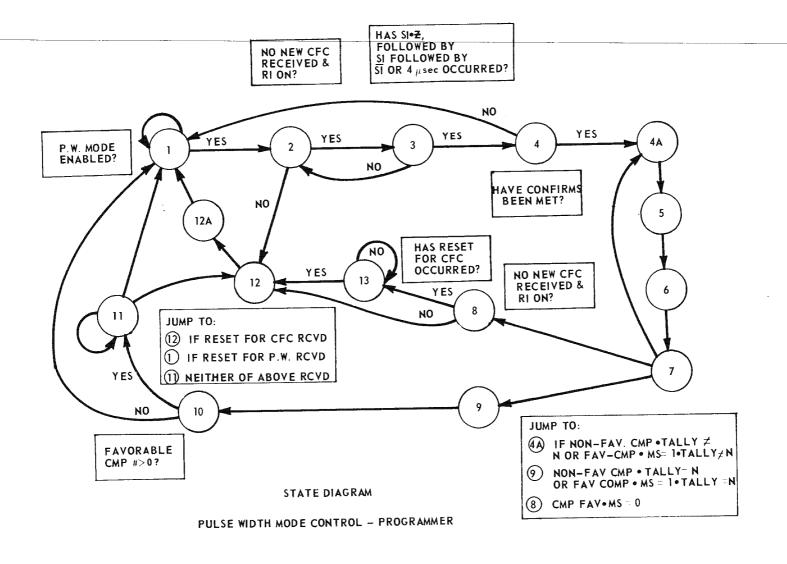

| 4.7-3      | Pulse Width Mode State Diagram      | 428        |

| 4.7-4      | PRI Mode State Diagram              | 429        |

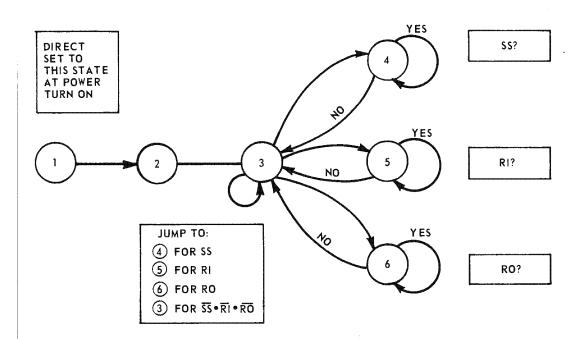

| 4.7-5      | Turn-On Control State Diagram       | 436        |

| 4.7-6      | Memory Instructions Timing Diagram  | 440        |

| 4.7-7      | Record Mode State Diagram           | 448        |

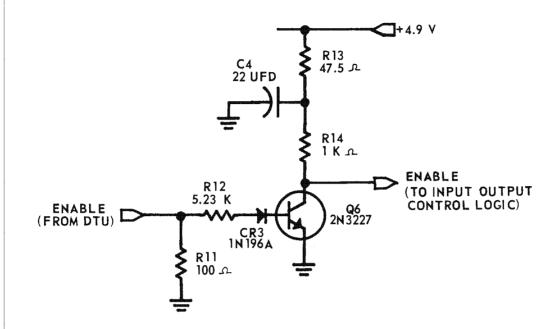

| 4.7-8      | Interface Enable                    | 454        |

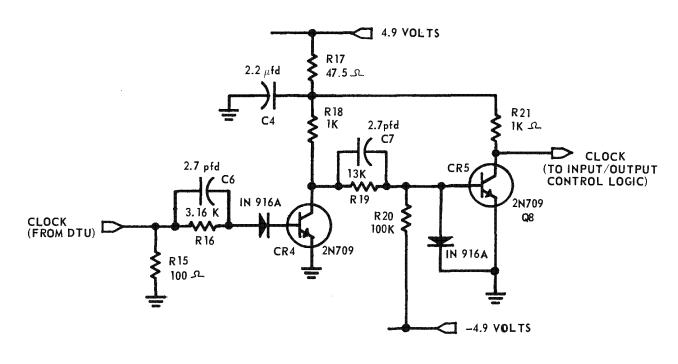

| 4.7-9      | Interface Clock                     | 455        |

| 4.7-10     | Data Interface                      | 456        |

| 4.7-11     | Relay Driver                        | 458        |

PANGLE VIA BYERRY CON-

SPECIAL HANDLING

Approved for Release: 2017/08/16 C05099935

52000-R500 Page xix

#### LIST OF FIGURES (Continued)

| Figure No. | Title                                  | Page |

|------------|----------------------------------------|------|

| 4.8-1      | Power Supply Overall Block Diagram     | 460  |

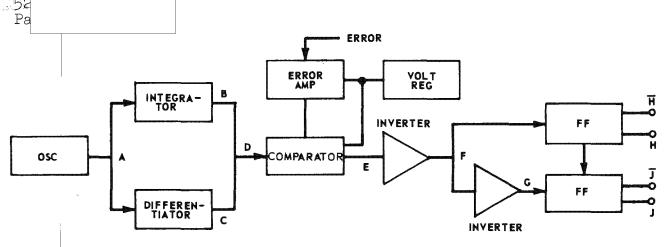

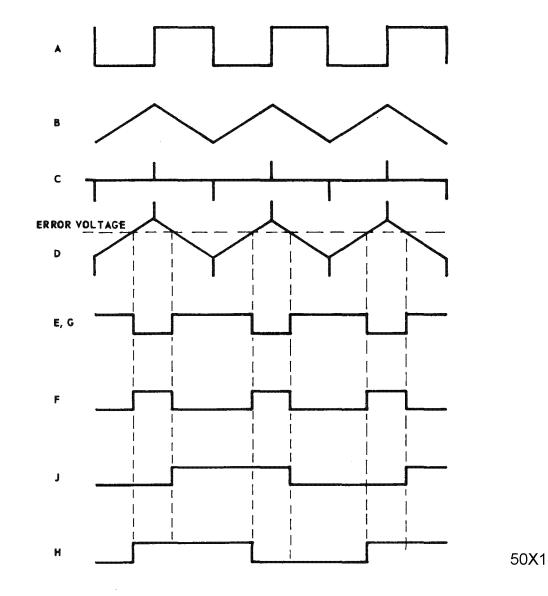

| 4.8-3      | Control Circuitry Waveforms            | 462  |

| 4.8-4      | Driver Transformers                    | 465  |

| 4.8-5      | High-Level Logic                       | 466  |

| 4.8-6      | High-Level Logic Waveforms             | 467  |

| 4.8-7      | Auxiliary Power Supply Block Diagram   | 471  |

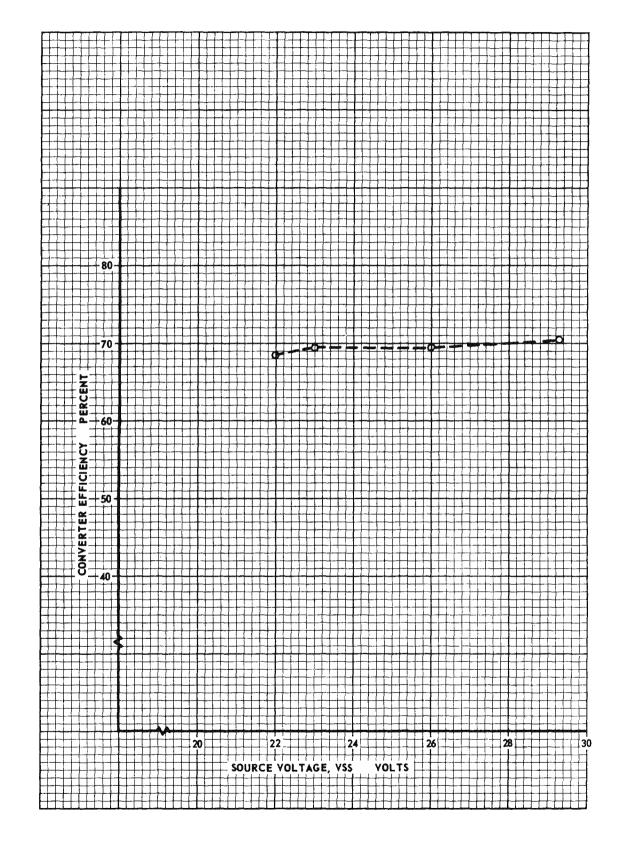

| 4.8-8      | Converter Efficiency vs Source Voltage | 475  |

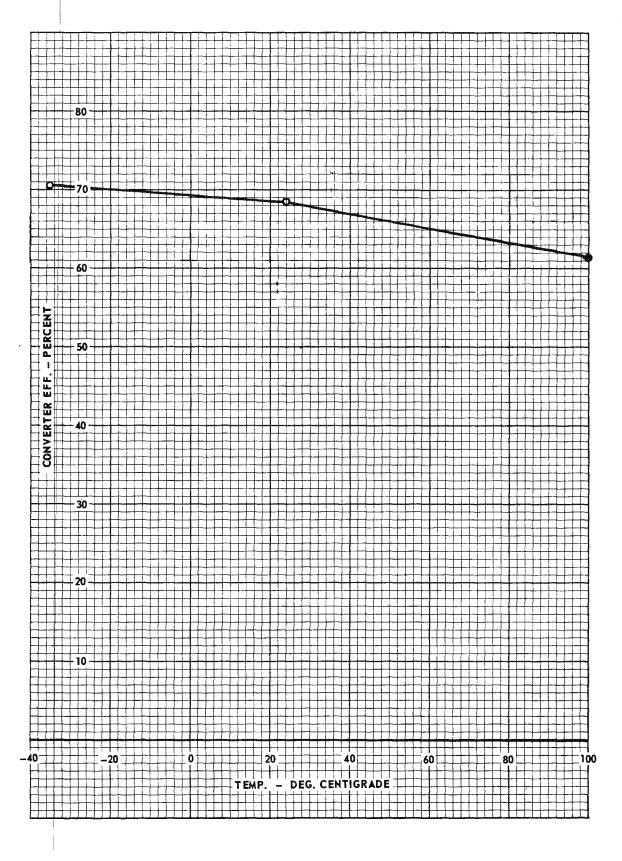

| 4.8-9      | Converter Efficiency vs Temperature    | 476  |

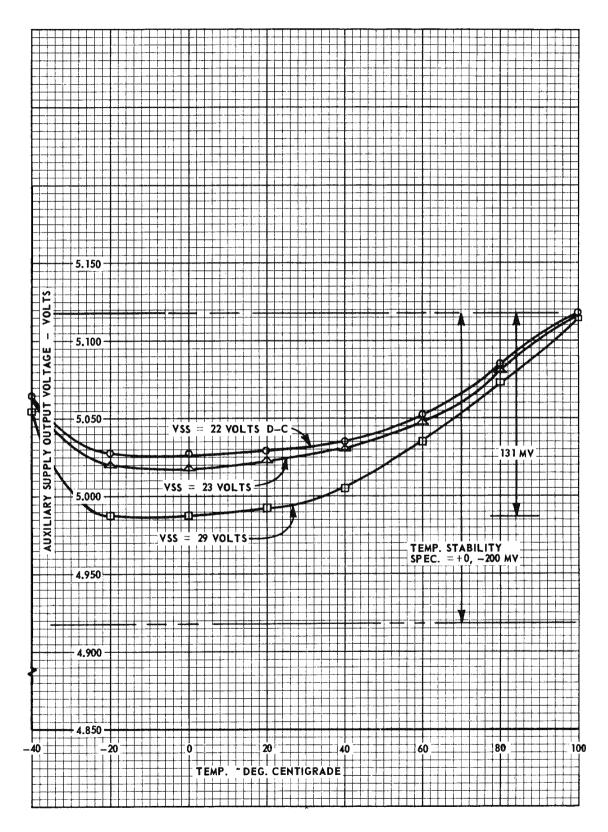

| 4.8-10     | Auxiliary Power Supply Output vs       |      |

|            | Temperature and Sourch Voltage         | 477  |

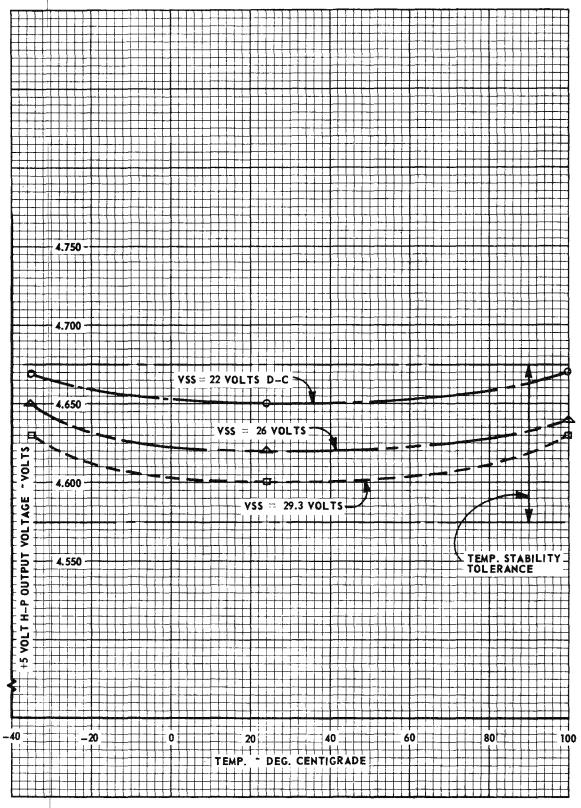

| 4.8-11     | +5-Volt Hing Power Output vs           |      |

|            | Temperature and Source Voltage         | 478  |

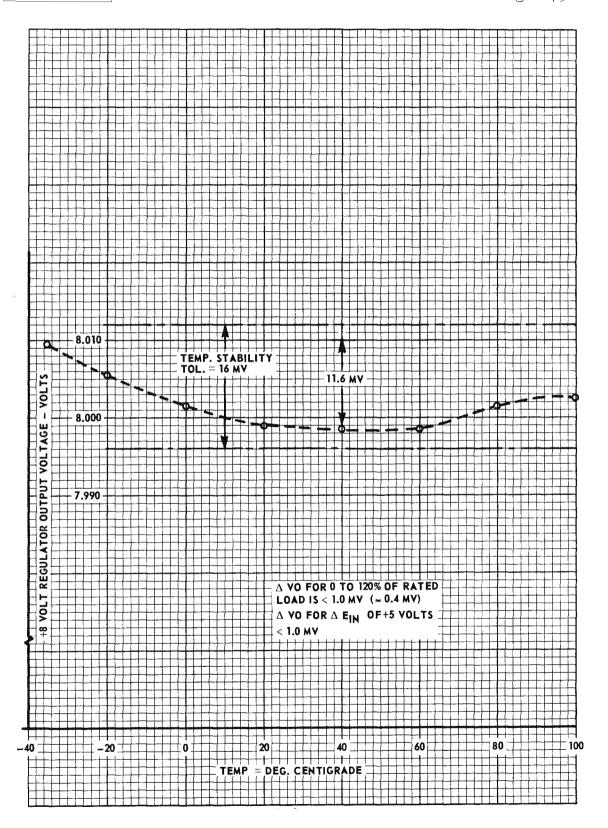

| 4.8-12     | Typical Regulator Output               | 479  |

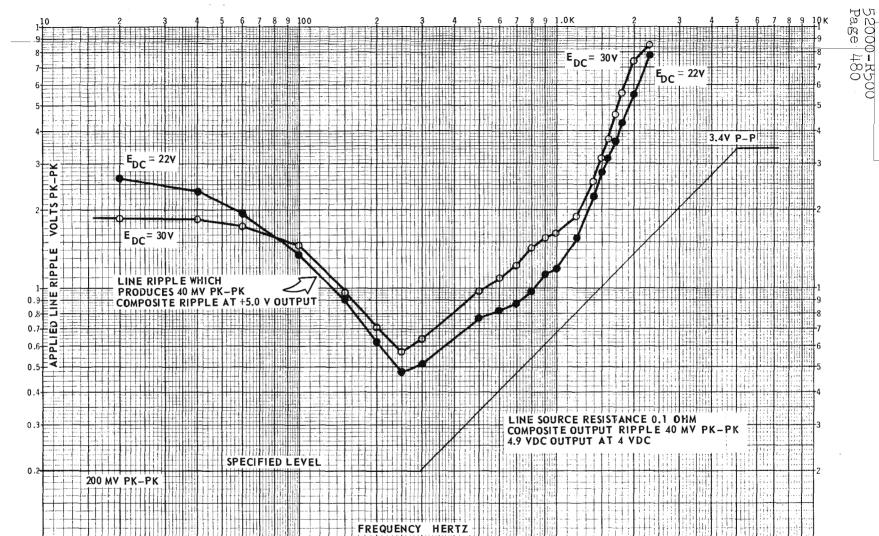

| 4.8-13     | Susceptibility Response                | 480  |

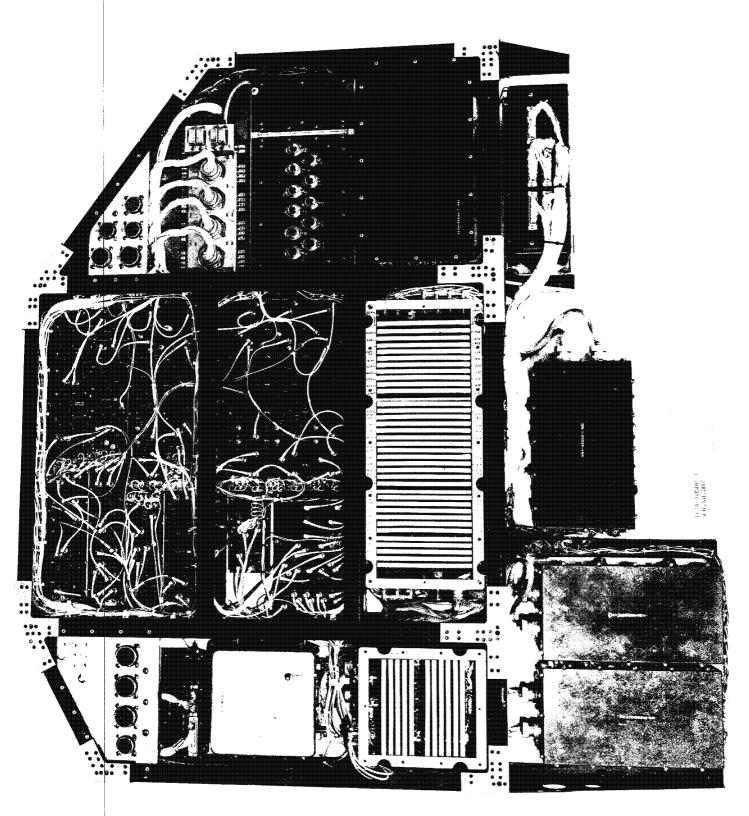

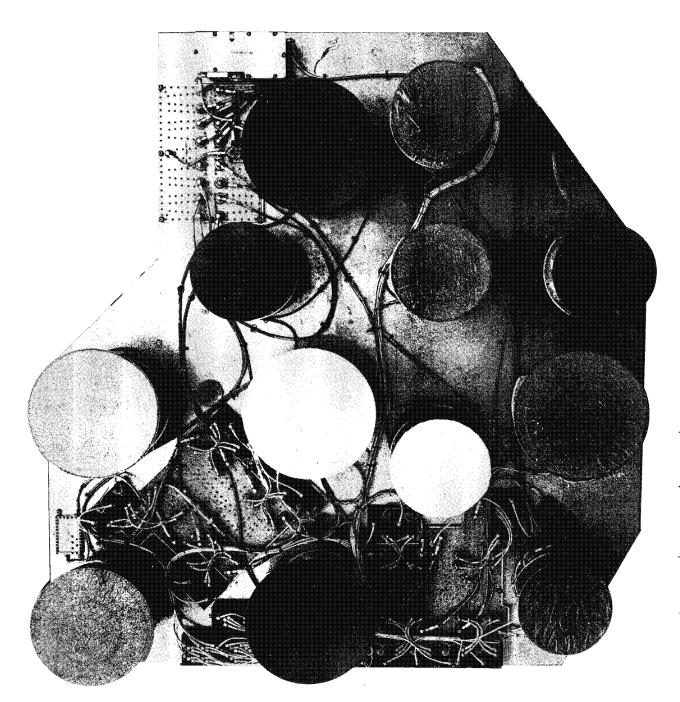

| 4.9-1      | Complete System                        | 482  |

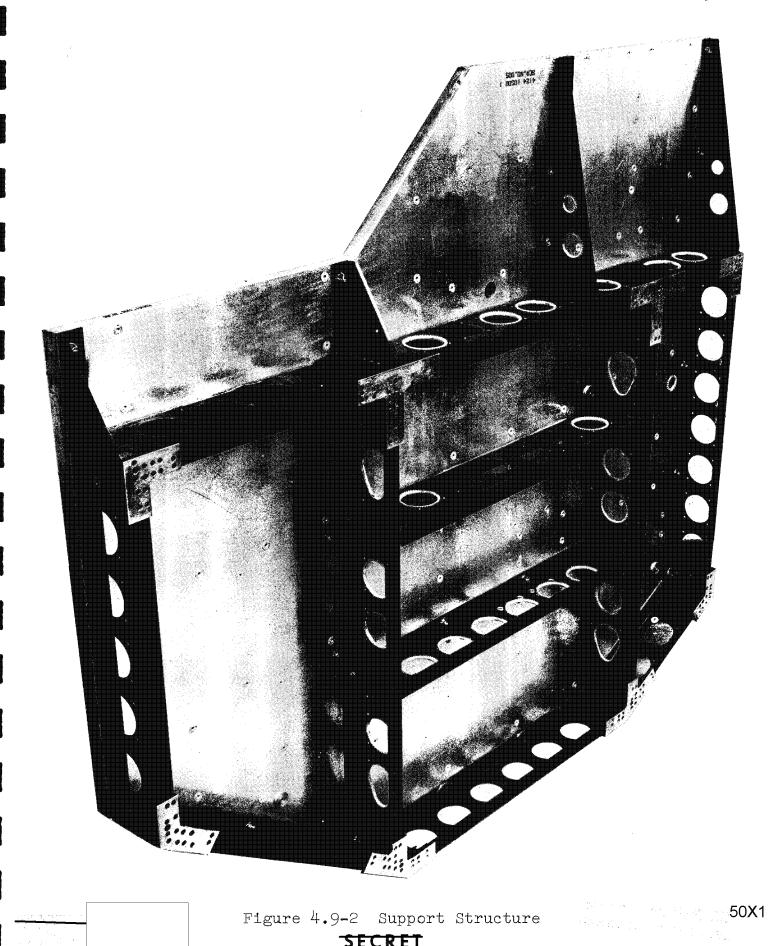

| 4.9-2      | Support Structure                      | 485  |

| 4.9-3      | Phase Horn                             | 486  |

| 4.9-4      | Spiral Antenna                         | 488  |

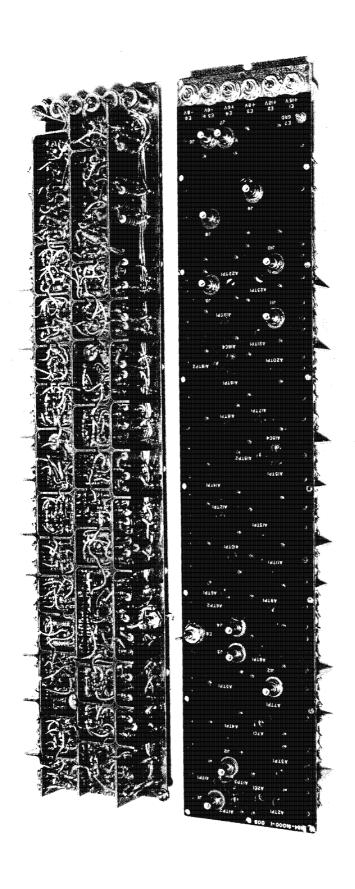

| 4.9-5      | IF Phase Channel                       | 489  |

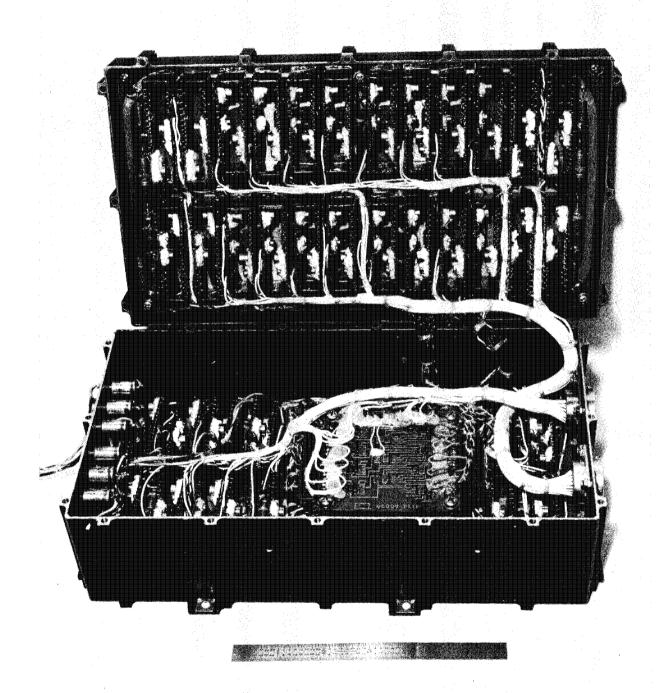

| 4.9-6      | Data Handler Housing                   | 492  |

| 4.9-7      | Data Handler Card                      | 492  |

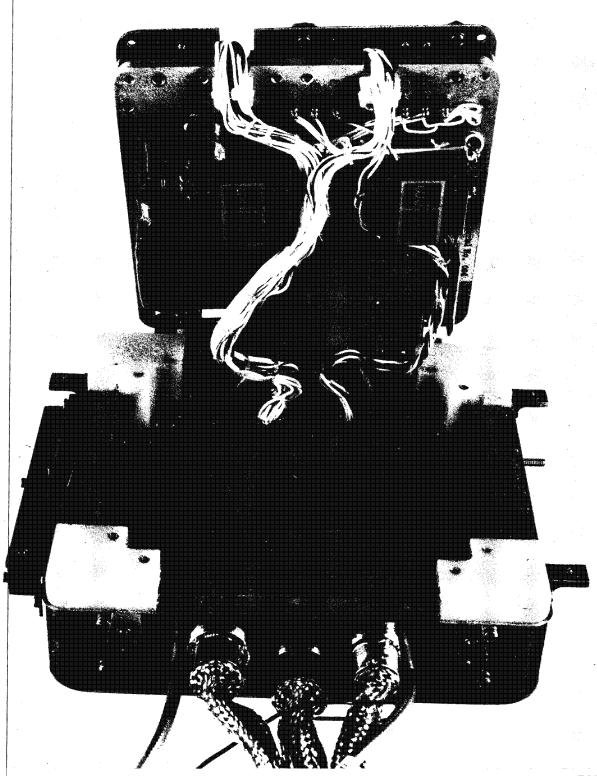

| 4.9-8      | Buffer Storage                         | 494  |

| 4.9-9      | Memory @ Cover Open                    | 495  |

# Approved for Release: 2017/08/16 C05099935 SPECIAL HANDLING

Page xx

LIST OF FIGURES (Continued)

| Figure No.              | Title                                  | <u>Page</u> |

|-------------------------|----------------------------------------|-------------|

| 4.10-1                  | System Thermal Finishes ON -Y Side     | 512         |

| 4.10-2                  | High Noon Orbit Schematic              | 520         |

| 4.10-3                  | Payload-PV Node Numbers                | 523         |

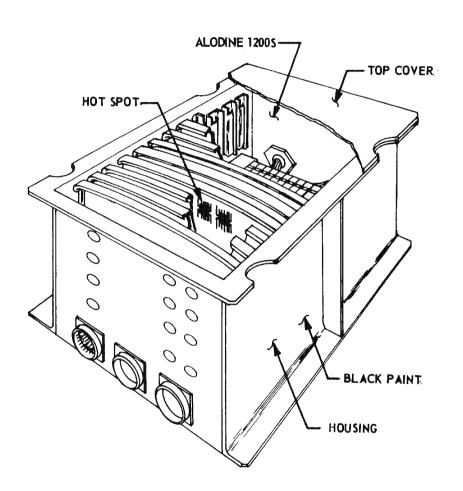

| 4.10-4                  | Data Handler No. 2 Thermal Layout      | 527         |

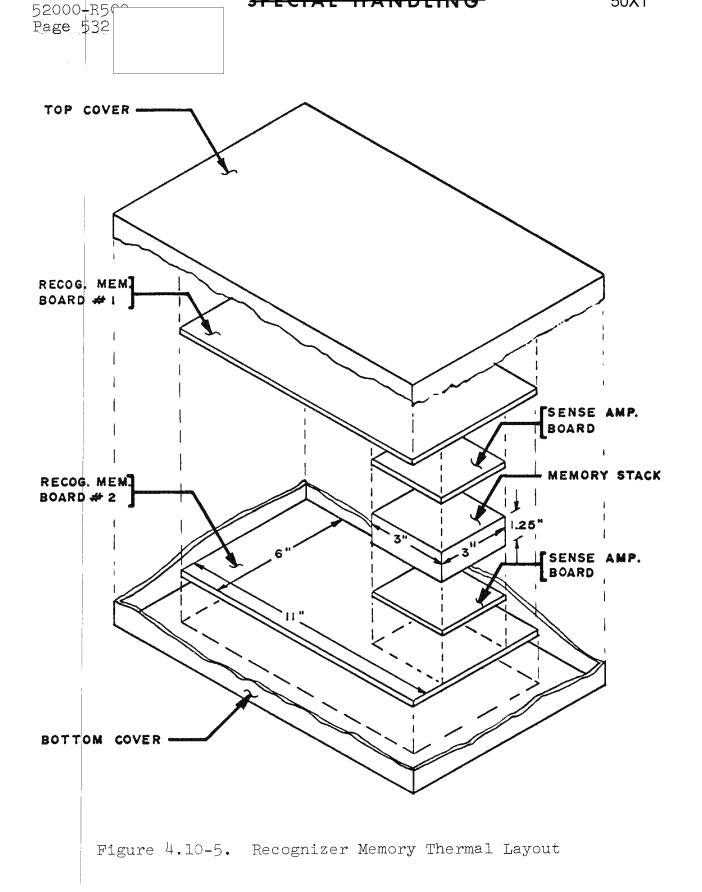

| 4.10-5                  | Recognizer Memory Thermal Layout       | 532         |

| 4.10-6                  | IF Phase Channel Thermal Layout        | 536         |

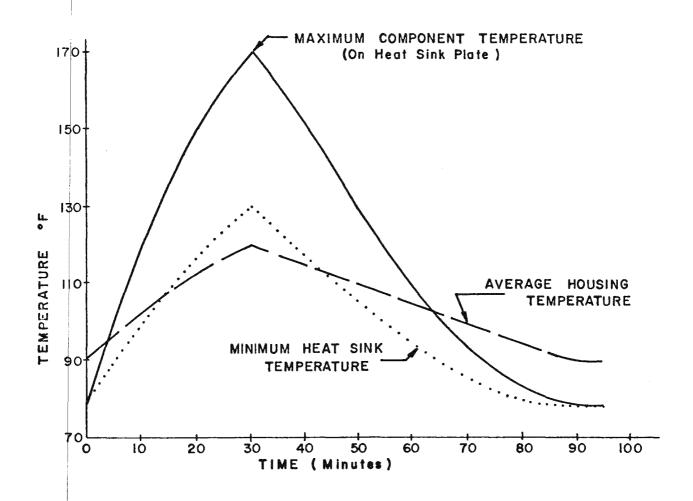

| 4.10-7                  | Power Supply Thermal Layout            | 539         |

| 4.10-8                  | Power Supply Transient Response-       |             |

|                         | Worst Case                             | 544         |

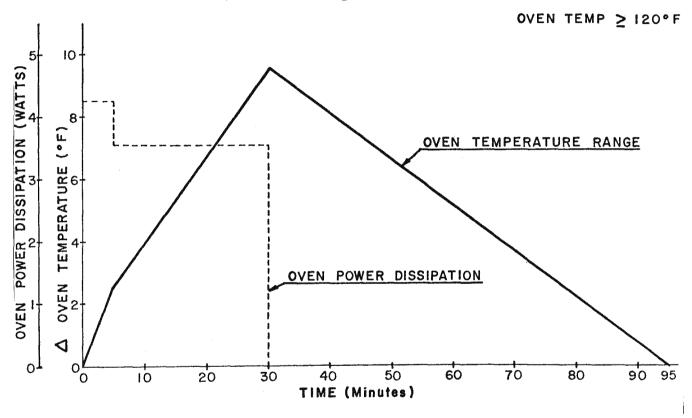

| 4.10-9                  | LO Oven Transient Temperature Response | 547         |

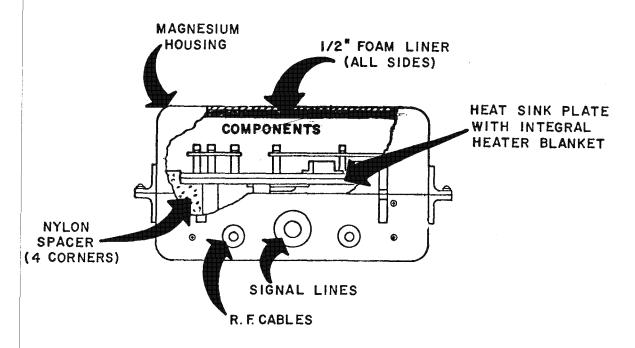

| 4.10-10                 | LO Oven Thermal Layout                 | 548         |

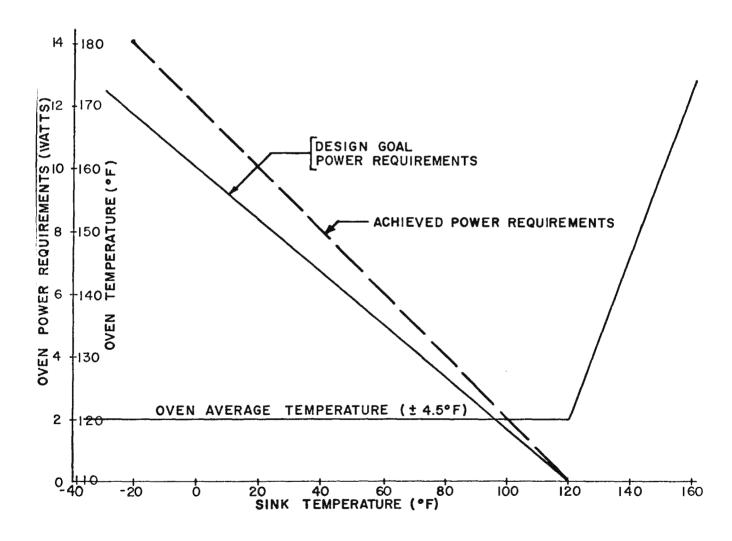

| 4.10-11                 | LO Oven Power Requirements             | 549         |

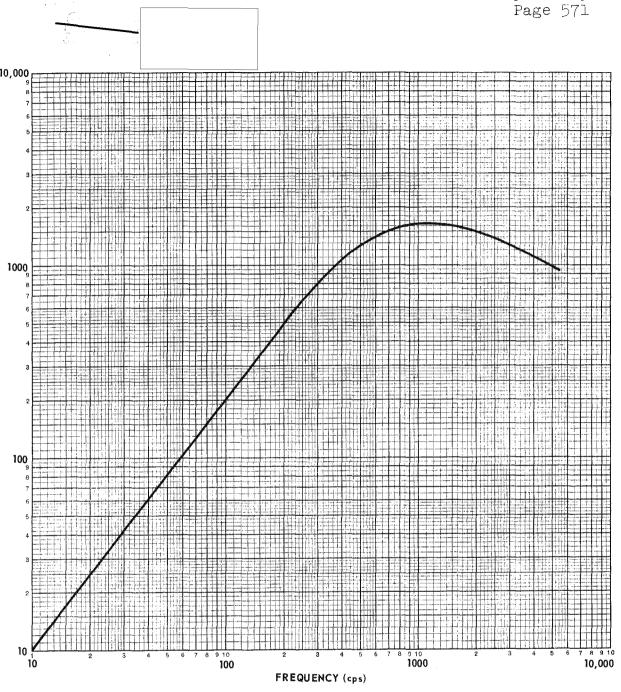

| 5 2-1                   | Pyrotechnic Shock Response Spectrum    |             |

|                         | (Q-10)                                 | 571         |

| 5 <b>-</b> 3 <b>-</b> 1 | Test Procedures                        |             |

| 6 4-1                   | Reliability Diagram                    | 591         |

| 6.4-2                   | Probability of Successful Operation    |             |

| 1                       | In Mode 1                              | 594         |

| 6.4-3                   | Probability of Successful Operation    |             |

|                         | In Mode 2                              | 595         |

| 7.1-1                   | Power Control Panel                    | 600         |

| 7.1-2                   | Command and Control Panel              | 602         |

| 7.1-3                   | BRO Panel                              | 613         |

|                         |                                        |             |

SPECIAL HANDLING

Approved for Release: 2017/08/16 C05099935

STANTON CANONING CONTRACTOR

52000-R500 Page xxi

#### LIST OF FIGURES (Continued)

| Figure No.              | <u> Title</u>            | <u>Page</u> |

|-------------------------|--------------------------|-------------|

| 7.1-4                   | DRO Panel                | 615         |

| 7.1-5                   | T/M Scanner Panel        | 617         |

| 7.1-6                   | Data Acquisition Console | 617         |

| 7.1-7                   | Printer                  | 618         |

| 7.1-8                   | Printer Control Panel    | 622         |

| 7.1-9                   | BDM/DTU Panel            | 622         |

| 7.1-10                  | RF Console               | 624         |

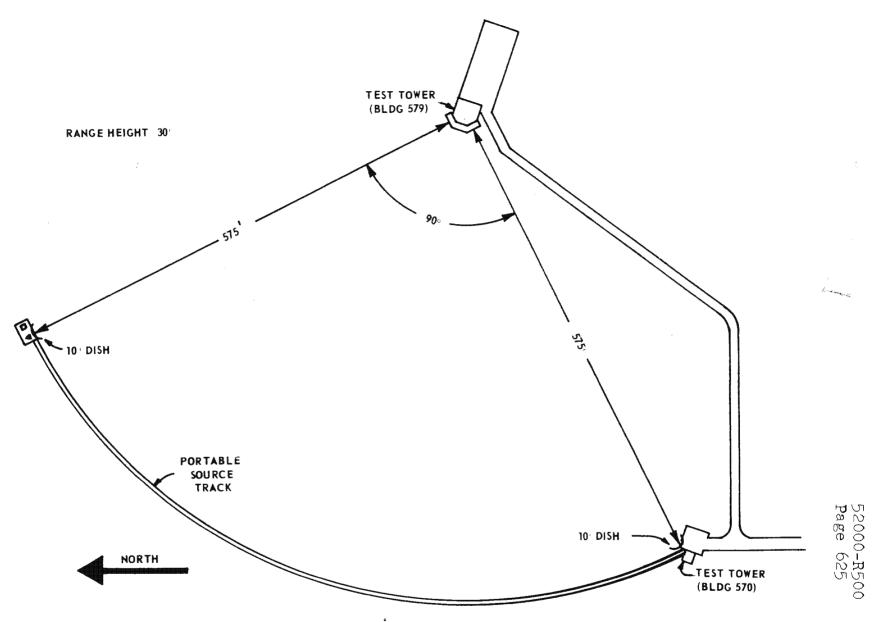

| 7.1-11                  | Test Range Plan View     |             |

| 7.1-12                  | Digitization Panel       | 627         |

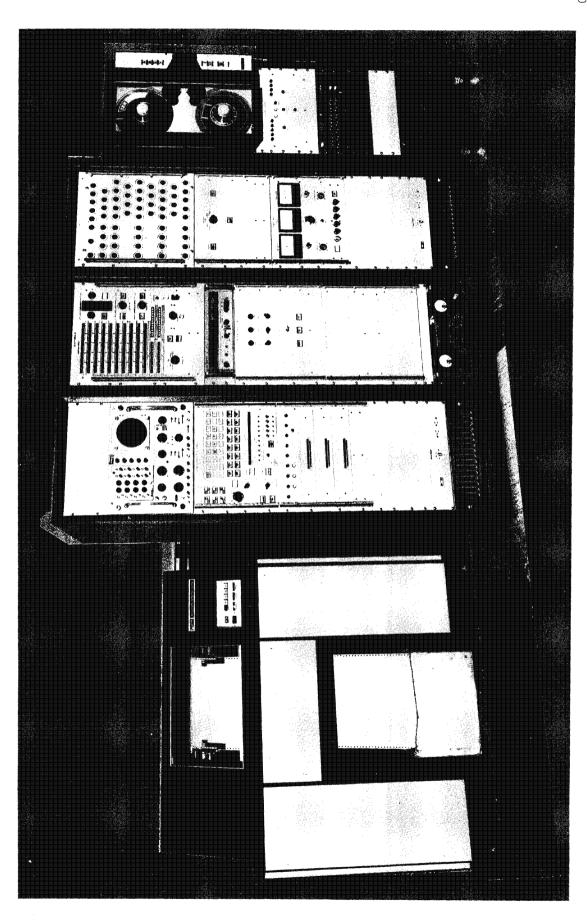

| 7.2-1                   | Ground Support Equipment | 629         |

| 7.2-2                   | Holding Fixture          | 630         |

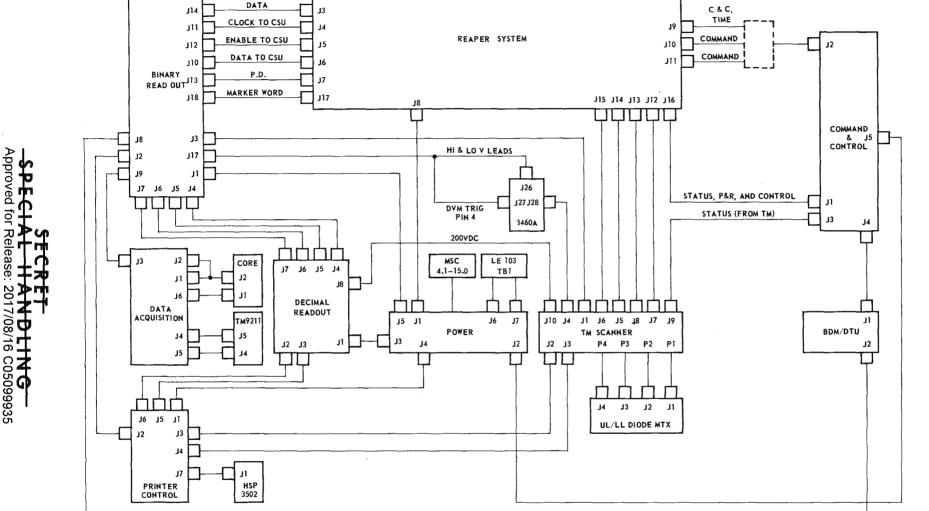

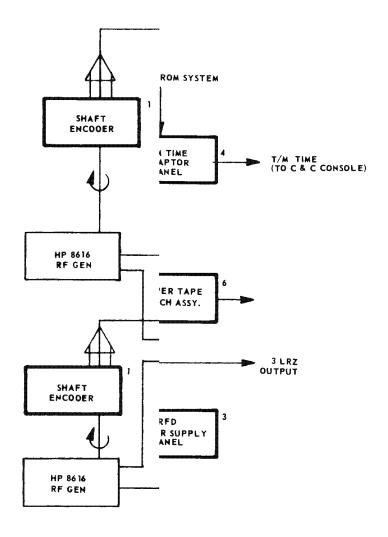

| 7 <b>.</b> 2 <b>-</b> 3 | Block Diagram            | 631         |

| 7.2-4                   | RF Console Block Diagram | 633         |

| 7 2 5                   | Positioner And Control   | 635         |

# Approved for Release: 2017/08/16 C05099935 SPECIAL HANDLING

Page xxii

#### LIST OF TABLES

| TABLE NO.              | TITLE                                            | PAGE |

|------------------------|--------------------------------------------------|------|

| 2.2-1                  | Recognizer Set Data                              | 14   |

| 2.2-2                  | Recognizer Output Modes                          | 15   |

| 2.3-1                  | Operational Modes                                | 19   |

| 2.3-2                  | Command Restriction Summary                      | 19   |

| <b>2.</b> 3 <b>-</b> 3 | Commands With No Restriction                     | 20   |

| 2.3-4                  | System Commands .                                | 21   |

| 2.3.2-1                | Recognizer Threshold                             | 35   |

| 2.4-1                  | Intercept Word Format                            | 41   |

| 2.4-2                  | Status Word Format                               | 42   |

| 2.4-3                  | Marker Word Format                               | 44   |

| 2.4-4                  | Recognizer Word Format                           | 45   |

| 2.5-1                  | Recognizer Output Modes                          | 50   |

| 3.3-1                  | Fine Phase Position Horizon-to-<br>Horizon       | 69   |

| 3.6-1                  | Predicted Electrical Phase Errors                | 78   |

| 3.6-2                  | Amplitude Error Analysis                         | 84   |

| 3.6-3                  | Reaper Frequency Error Budget (Worst Case)       | 87   |

| 4.1-1                  | Antenna Characteristics                          | 101  |

| 4.2-1                  | RF Bandpass Filter Electrical<br>Characteristics | 124  |

| 4.2-2                  | Electrical Performance Specifications RFCO       | 131  |

| 4.2-3                  | Summary of Main Stripline Performance            | 144  |

| 4.3-1                  | Local Oscillator Performance<br>Characteristics  | 149  |

SPECIAL HANDLING

Approved for Release: 2017/08/16 C05099935

52000-R500

50X1

#### LIST OF TABLES (CONT'D)

| TABLE NO.               | TITLE                                                      | PAGE |

|-------------------------|------------------------------------------------------------|------|

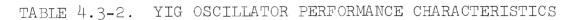

| 4.3-2                   | YIG Oscillator Performance<br>Characteristics              | 151  |

| 4.3-3                   | Current Driver Performance<br>Characteristics              | 153  |

| 4.3-4                   | D/A Converter Performance<br>Characteristics               | 156  |

| 4.3-5                   | Reference Voltage Regulator<br>Performance Characteristics | 157  |

| 4.3-6                   | Temperature Controller Performance<br>Characteristics      | 160  |

| 4.4-1                   | Frequency Deviation Versus<br>Temperature                  | 165  |

| 4.4-2                   | Spectrum Power Versus Temperature                          | 165  |

| 4.5-1                   | Preamplifier Specifications                                | 172  |

| 4.5-2                   | Signal Combiner Specifications                             | 174  |

| 4 <b>.</b> 5 <b>-</b> 3 | Hybrid Subassembly Specifications                          | 176  |

| 4.5-4                   | Preamp Switch Specification                                | 177  |

| 4 <b>.</b> 5 <b>-</b> 5 | IF Phase Channel Specifications                            | 195  |

| 4.5-6                   | IF Phase Channel C Specifications                          | 197  |

| 4.5-7                   | Frequency Confirm Specifications                           | 203  |

| 4.5-8                   | Log IF Amplifier Specifications                            | 211  |

| 4.5-9                   | SI Control Truth Table                                     | 216  |

| 4.5-10                  | SI Generator Specifications                                | 218  |

| 4.5-11                  | A/R and PW Confirm Specifications                          | 228  |

| 4.5-12                  | Real-Image Logic Specification                             | 236  |

MANDER OF BREWER COMPANY THOREM ONEN

# 52000-R500 Page xxiv

## Approved for Release: 2017/08/16 C05099935

#### **SPECIAL HANDLING**

50X1

#### LIST OF TABLES (CONT'D)

| TABLE NO. | TITIE                                         | PAGE |

|-----------|-----------------------------------------------|------|

| 4.5-13    | TTS Subassembly Specifications                | 245  |

| 4.5-14    | Recognizer Amplitude-Threshold Specifications | 249  |

| 4.5-15    | Input Voltage vs. Output Code                 | 254  |

| 4.5-16    | A/D Converter Specifications                  | 258  |

| 4.6.1     | Combiner Error Detector Operator              | 272  |

| 4.6.2     | Phase Coder Ambiguity Removal Logic           | 278  |

| 4.6-3     | 3 LRZ Converter                               | 362  |

| 4.6-4     | Marker Word Format                            | 367  |

| 4.6-5     | System Commands                               | 387  |

| 4.6-6     | Telemetry Points                              | 391  |

| 4.7-1     | Record Time                                   | 450  |

50X1

Approved for Release: 2017/08/16 C05099935

52000-R500 Page xxv

(Left Blank Intentionally)

SPECIAL HANDLING

Approved for Release: 2017/08/16 C05099935

CONTROL SYSTEMS ONLY

Approved for Release: 2017/08/16 C05099935

SPECIAL HANDLING

50X1

52000-R500 Page xxvi

(To Be Published In Final Report)

REAR

Reaper System Figure 1.1-1.

52000-R500 Page 1

#### 1.0 INTRODUCTION

#### 1.1 Scope

This report describes the engineering development of an electromagnetic reconnaissance system, designated "Reaper." The subject matter is organized in the following manner. First, a system description and analysis presents the details of system development. System components are then described. Design analyses in the areas of mechanical design, radio-frequency interference, test, and reliability follow the component descriptions. Ground support test equipment is described in general terms.

Previously published analyses are not included in this report. Reference is made to Technical Description Report for Setter IB System, Document No. 52000-R378, dated 10 January 1967 for information relative to previously developed systems.

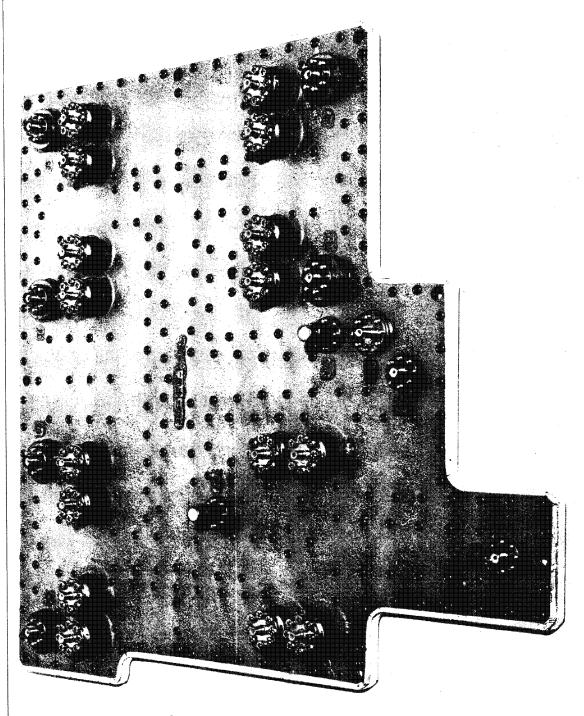

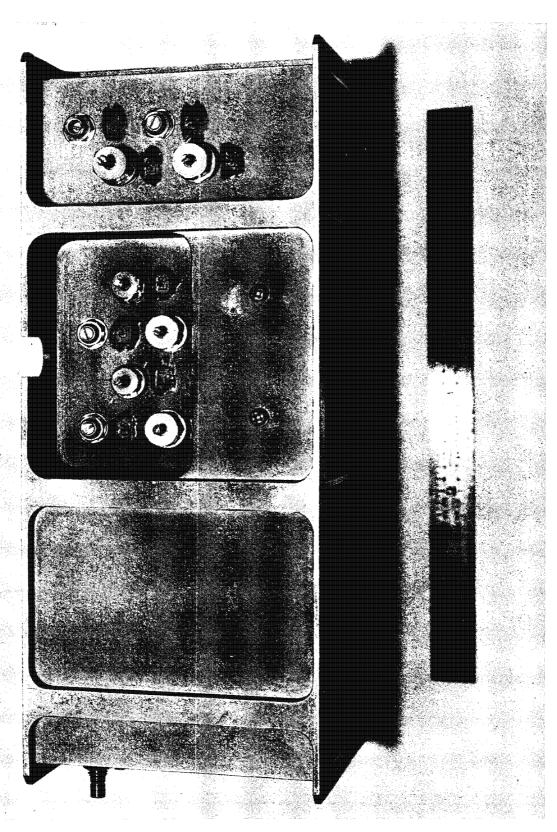

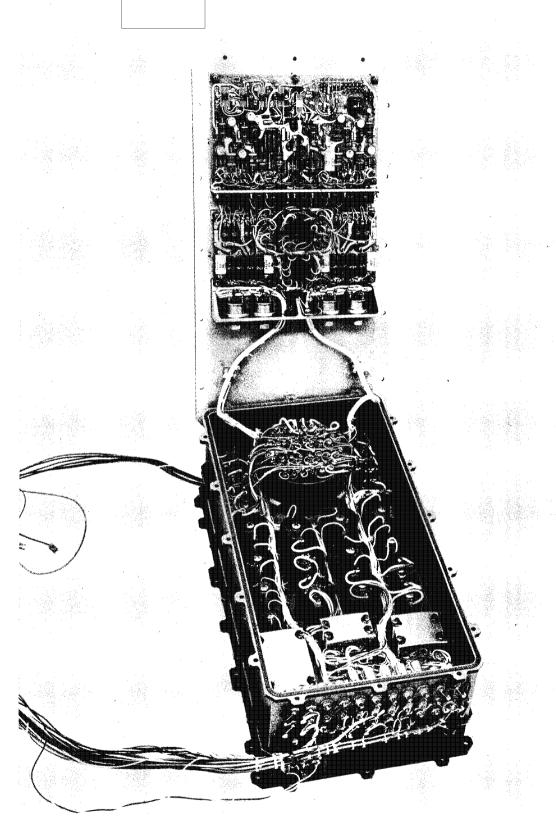

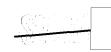

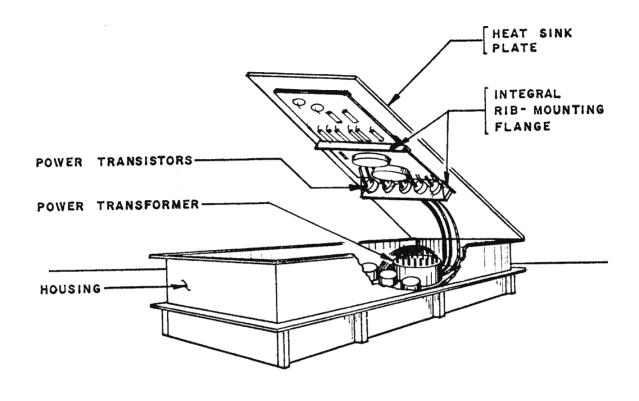

Figure 1.1-1 illustrates system hardware.

#### 1.2 Summary

Reaper is an advanced electromagnetic-emitter locating system designed to be operated from an earth-orbiting The equipment mates with an Agena vehicle and system platform. interface is compatible with Payload Vehicle Digital Command Programmer, Type 20, as defined by LMSC Specification No. AA11654-3.

Normal dwell time is such that emitters in general service are analyzed four times in the time required for the system field-of-view to pass over a target. The number of emitters and the duration of the emitter pulse repetition interval determine whether a 2-, 3-, or 4-pulse analysis will be made.

Two major modes of operation are provided. The electronic order-of-battle mode provides emitter direction-finding and parameter measurements of frequency, pulse width, pulse repetition interval and pulse amplitude. The technical-intelligence mode provides specific comparisons of processed data to stored data, enables a stop-scan condition, and supplies a pre-detected output for analog recording.

Frequency range of the system is from 1800 MHz to 3300 MHz. Frequency sampling is accomplished in increments of 2.5 MHz.

Two dwell modes are provided. In the normal dwell mode, four successive pulses with an interval of 5.28 ms or less are processed in a single dwell time. Normal dwell time is such that at least two "looks" are completed in the time required for the system field of view to pass over a target.

An alternate dwell mode provides a dwell time twice that of the normal mode. The long dwell time enables analysis of special emitters which have long pulse repetition times.

#### SPECIAL HANDLING

**50X1**

52000**-**R500 Page 3

The system operates at an altitude of 268 nautical miles and an orbit inclination of 75°. Vehicle orientation is such that the Y-axis of the field-of-view is in the direction of flight. Under normal flight conditions, the cross-track field-of-view is at least 160 nautical miles wide and the intrack field-of-view is large enough to provide two scans of each target in normal target density environments.

Orbital lifetime of the system is six months under normal programming conditions. Normal programming consists of 90 hours of intermittent operation, maximum, per month with a 30-minute, maximum, operating period per orbit.

#### 2.0 SYSTEM DESCRIPTION

The Reaper system is an advanced electromagnetic emitter location system designed to be operated from an orbiting platform as part of the Strawman payload. The system is principally a precision direction-finding payload with the added capability of precise measurement of the emitter pulse parameters of frequency, pulse width, pulse repetition interval, and pulse amplitude. The system's normal Electronic Order of Battle (EOB) capability is further enhanced by a programmable technical intelligence (TI) capability.

#### 2.1 EOB Functions

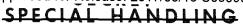

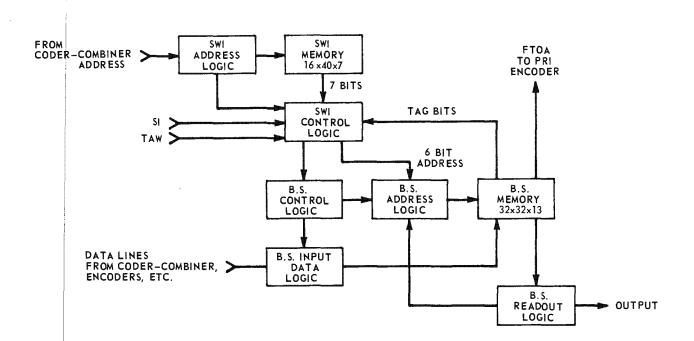

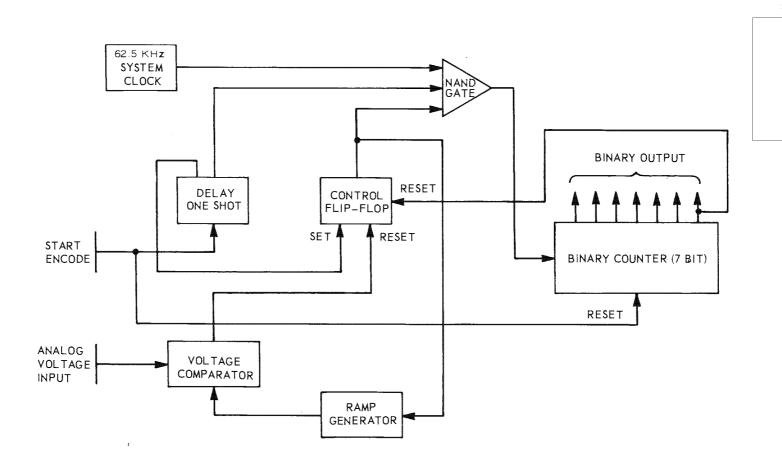

The system gathers parameter data on electromagnetic signals recieved over the RF range of 1800-3300 MHz, processes the data into digital form and transfers it to a core storage unit in the payload vehicle. The following paragraphs describe the exact frequency coverage, receiver sensitivity, ground coverage, signal processing and confirm-inhibit criteria. A block diagram of the system is shown in Figure 2.1-1.

#### 2.1.1 Frequency Coverage

#### 2.1.1.1 Normal Scan

The system local oscillator is sequentially stepped through the RF range in 2.5 MHz steps from the low frequency limit to the high frequency limit. Digital logic circuitry controls the stepping (scanning) and causes the receiver to dwell at each step for a certain period of time. During each

52000-R500 Page 7

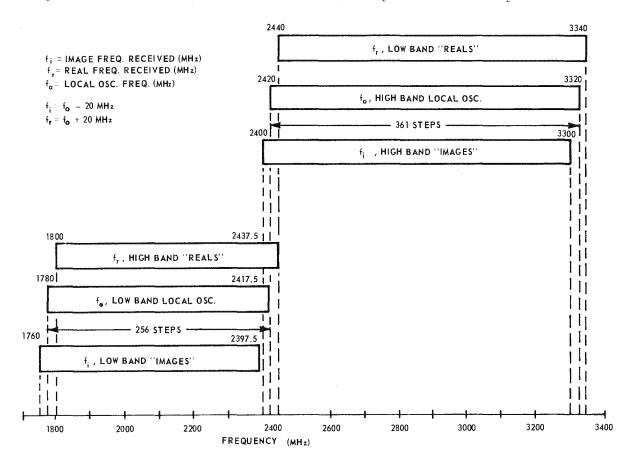

dwell period, the system accepts and processes those signals which meet the confirm-inhibit criteria described in paragraph 2.1.4. The resulting RF coverage is shown in Figure 2.1-2.

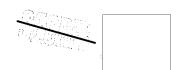

The dwell period at each frequency step is a function of the number of received signals. If no confirmed signals are received in the basic dwell period (search time) of 6.14 milliseconds, the local oscillator is moved to the next higher step and a new dwell started. If a confirmed signal is received during the search time, the dwell is lengthened to 22.5 milliseconds to allow additional pulses to be processed.

FREQUENCY COVERAGE FIGURE 2.1-2

08/16 C05099935

50X1 Severate the Claresia

Garrage et en en en etale

50X1

The variation in dwell time results in a variable scan time to cover the RF range. Figure 2.1-2 shows the variation in scan time as a function of the number of steps yielding at least one confirmed pulse. An alternate dwell mode is available by command with a search time of 22.5 milliseconds extended to 45 milliseconds with a confirmed pulse. The scan time resulting from the alternate dwell is also shown in Figure 2.1-3.

An alternate frequency scan mode is available, by command, to allow covering only one or two segments of the RF range and not scanning the remainder. The segment limits are stored in a memory and can be reprogrammed on orbit. Any two segments of the "real" range shown in Figure 2.1-2 can be selected in the partial scan mode, within the restrictions given in paragraph 2.3.1.1.5.

#### 2.1.2 <u>Ground Coverage</u>

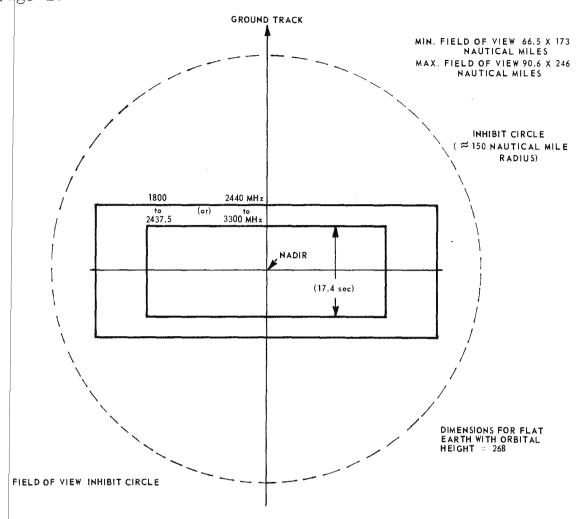

The system sorts signals by location and only accepts for Electronic Order of Battle (EOB) processing those from locations within a rectangular field-of-view centered about the vehicle nadir. The field-of-view varies in size with signal frequency as illustrated in Figure 2.1-4. As shown in the illustration, the rectangular field-of-view is surrounded by an inhibit circle which prevents EOB processing of signals received from large angles off the vehicle vertical axis. Either function can be selected by command.

52000-R500 Page 9

FIGURE 2.1-3 SCAN TIME

#### 2.1.3 Sensitivity

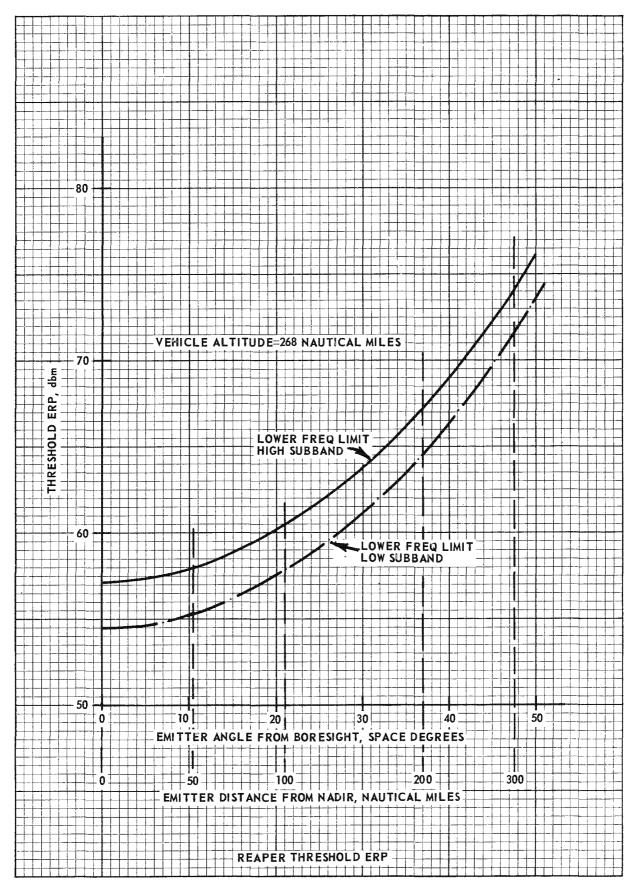

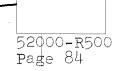

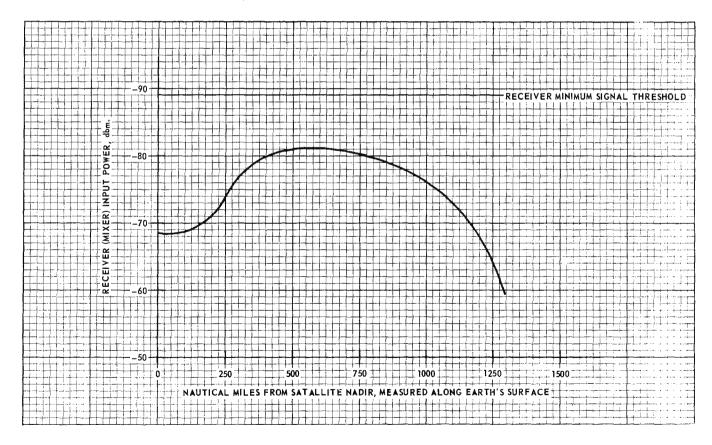

Figure 2.1-5 shows the typical minimum effective radiated power required for EOB processing as a function of distance from the nadir. This value can be adjusted downward (less sensitive) in two 5-db steps by command.

#### 2.1.4 Signal Processing

2.1.4.1 Processing Sequence

During a dwell period, if a signal (pulse or CW)

SPECIAL

52000-R500 Page 10

FIGURE 2.1-4 FIELD-OF-VIEW IMHIBIT CIRCLE

ments of the signal amplitude, frequency, width, repetition rate and angle of arrival are initiated, and digital processing begins. Encoding of the analog data proceeds while the confirm-inhibit decisions are made to establish that the signal is one for which output data is desired. When the analog measurements are completed, the associated circuitry is blanked from accepting further signals until digital processing is com-

52000-R500 Page 11

FIGURE 2.1-5 THRESHOLD ERP

OF CAME.

SPECIAL HANDLING Approved for Release: 2017/08/16 C05099935 50X1

PROPERTY OF THE SECTION

CONTRACTOR CONTRACTOR

50X1

52000-R500 Page 12

If an inhibit decision is made, digital processing stops, the digital circuitry is reset, the analog circuitry unblanked and the dwell continues. If the signal is not inhibited, the set of measured data is temporarily stored in a memory while other signals are processed.

If two, three, or four sets of data are taken from the same location during a dwell, the sets are grouped into a digital word and transferred to the vehicle storage. If only one set of data is taken on a signal, the data is discarded.

CW signals are processed by automatically resetting when the "pulse width" is measured and found to be greater than 24 microseconds. Pulse signals can be detected in the presence of CW by an automatic threshold adjustment which allows the pulse to be processed if it is at least 15 db above the CW level.

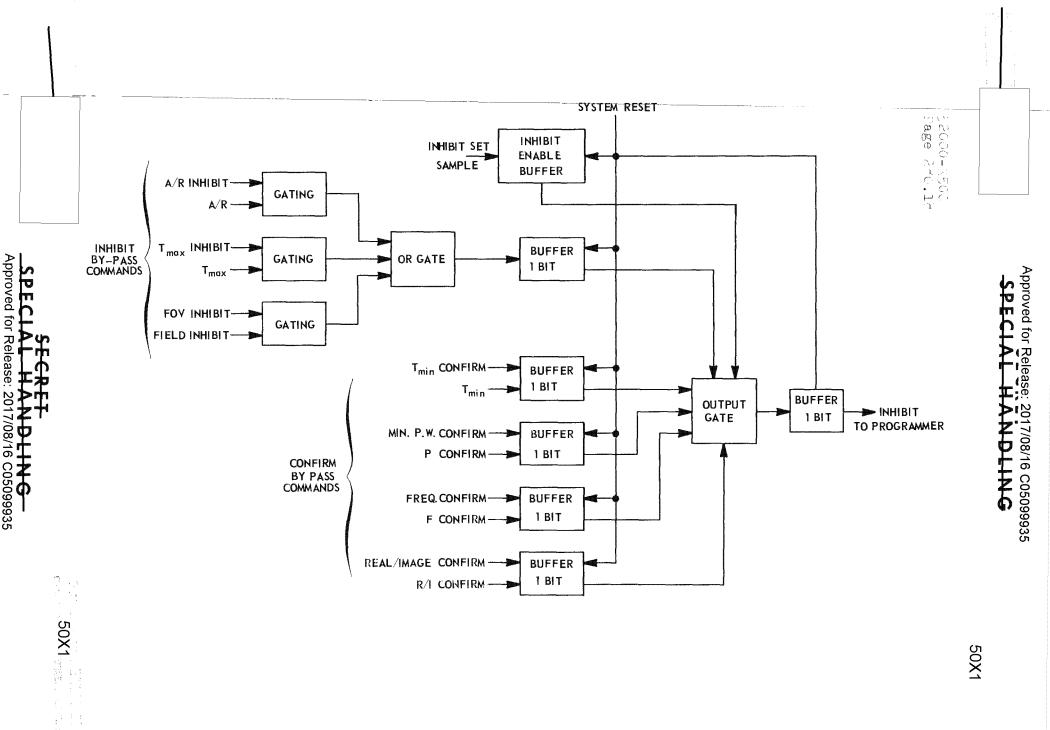

2.1.4.2 Confirm-Inhibit Decisions

The following functions are accomplished on each detected signal to eliminate undesired data and inaccurate measurements. Each of these functions can be separately disabled by command.

- a) Minimum Threshold Confirm Establishes that the signal being processed is above the minimum amplitude level required for accurate parameter measurements.

- b) Frequency Confirm Establishes that the signal is within the center portion (20  $\pm$  1.5 MHz)

50X1

HANDLE WA BYEMAN!

18 884.8

52000-R500 Page 13

of the receiver IF bandwidth.

- c) Real/Image Confirm Establishes that the signal is a real or that it is an image.

- d) Minimum Pulse-Width Confirm Establishes that the signal duration is equal to or greater than 0.4 microseconds.

- e) Pulse-Count Inhibit Allows a target from a particular direction to be processed only four times (four pulses) during a dwell.

- f) Field-of-View Inhibit Limits signal processing to those signals received from within the rectangular field of view.

- g) Amplitude-Ratio Inhibit Inhibits processing of signals arriving at large angles off boresight.

### 2.2 <u>Technical Intelligence Functions</u>

The system can be commanded to operate in a recognition mode while operating in parallel with the normal EOB processing. The purpose of the recognition mode is to detect and identify signals having parameters within certain ranges and interrupt the frequency scan to enable predetection recording of these signals on the vehicle DSU. In the recognition mode, basic operation is controlled by the EOB frequency scan. No change in normal EOB operation takes place until a signal is recognized.

SPECIAL HANDLING

pproved for Release: 2017/08/16 C05090935

<del>CIAL HANDLING</del>

52000-R500 Page 14

#### 2.2.1 Recognition Mode Signal Processing

At each frequency step (dwell), signals being processed by the EOB circuitry are also processed by the recognition circuitry. The EOB confirm-inhibit decisions of paragraph 2.1.4.2 are used to limit the amount of data available for recognition. The amount of data is restricted further by an additional minimum amplitude threshold which is commandable to one of four positions always at or above the EOB minimum threshold. Data from signals which meet the confirminhibit requirements are compared to parameter data stored in a P/L memory. The parameter data consists of eight sets with each set containing the information shown in Table 2.2-1. Each set is separately enabled by command and the entire memory contents can be reloaded in flight.

TABLE 2.2-1 RECOGNIZER SET DATA

|                      | LSB       | Limits                 | No. of Bits |

|----------------------|-----------|------------------------|-------------|

| Horizon or FOV mode: | ****      | _                      | 1           |

| Signal Parameters:   |           |                        |             |

| Frequency            | 5 MHz     | 1,800 MHz<br>3,300 MHz | 9           |

| Pulse Width          | 250 nsec. | 0.4 usec               | 4           |

|                      |           | 4 usec                 | 4           |

| PRI                  | 64        | 100 usec               | 7           |

|                      |           | 8,192 usec             | 7           |

| Record Mode:         |           |                        | 3           |

52000-R500 Page 15

Signal data is compared sequentially to parameters from each of the enabled stored sets. If a set is enabled in the horizon-to-horizon mode, only frequency ("reals" only) and pulse width are compared. In the field-of-view mode, pulse repetition interval is also compared. If a match is achieved between stored and measured data, the EOB scan operation is interrupted and the output mode specified in the matched set's data is executed. Table 2.2-2 shows the six output modes which can be selected.

| TABLE | 2.2-2 | RECOGNIZER                       | ULLGLILLO | MODES       |

|-------|-------|----------------------------------|-----------|-------------|

|       | C . C | 17 17 ( // 20 T 12 1 2 ) 17 17 1 |           | - パリシカフリールン |

| MODE     | WAIT TIME* | RECORD TIME |

|----------|------------|-------------|

| 1        | 0          | 2 SEC       |

| 2        | 0          | 4 SEC       |

| 3        | 0          | 8 SEC       |

| <u>1</u> | 60 SEC     | 4 SEC       |

| 5        | 60 SEC     | 8 SEC       |

| 6        | 60 SEC     | 300 SEC     |

\*If DSU not available.

#### 2.2.2 Predetected Signal Output

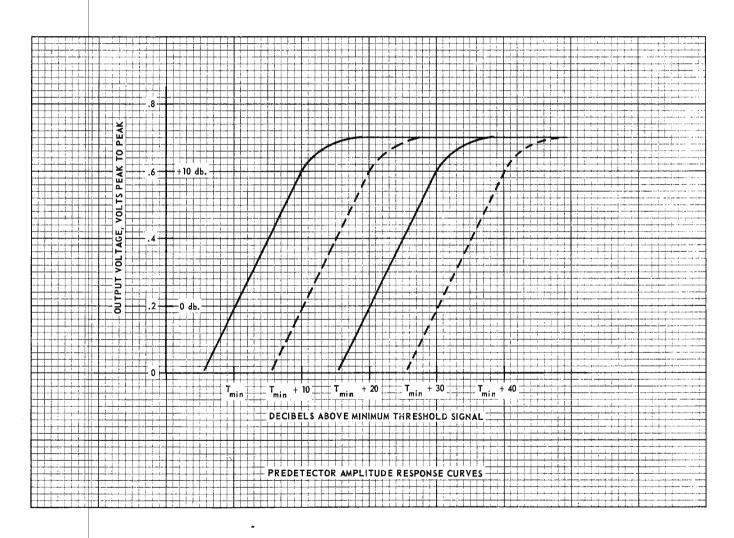

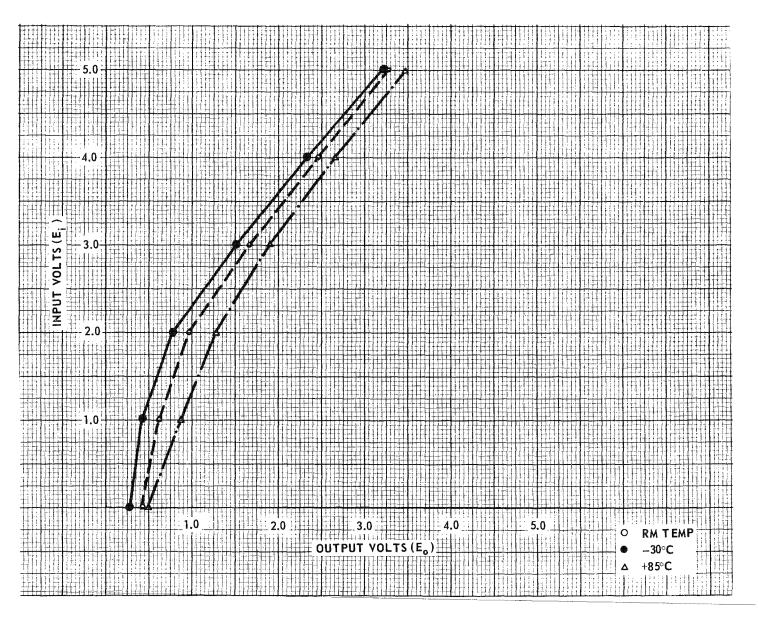

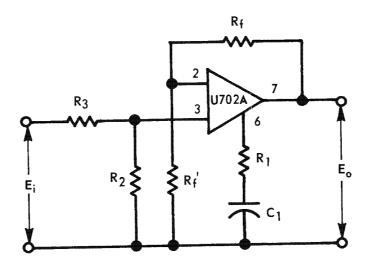

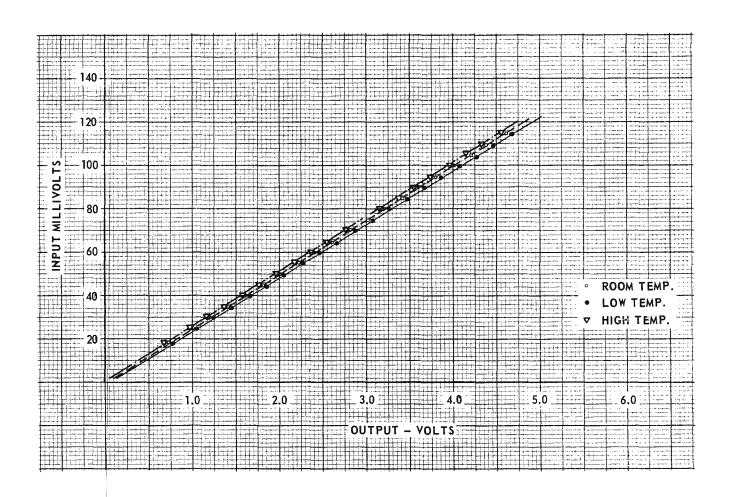

A predetected signal output is available at the vehicle interface for analog recording. The predetected signal preserves the RF signal characteristics within the limitations of the local oscillator and receiver bandwidth. The amplitude response is automatically adapted when a recognition

52000-R500 Page 16

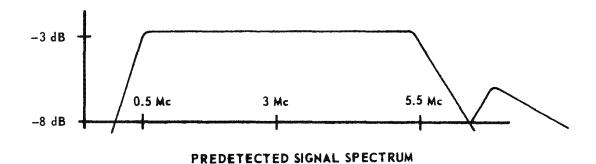

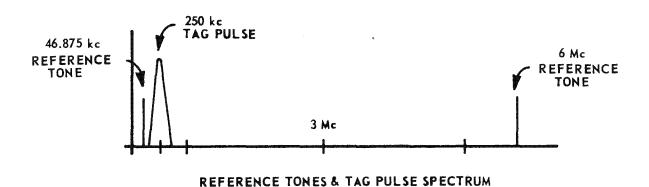

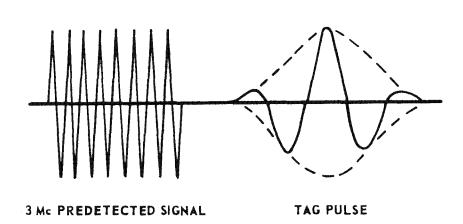

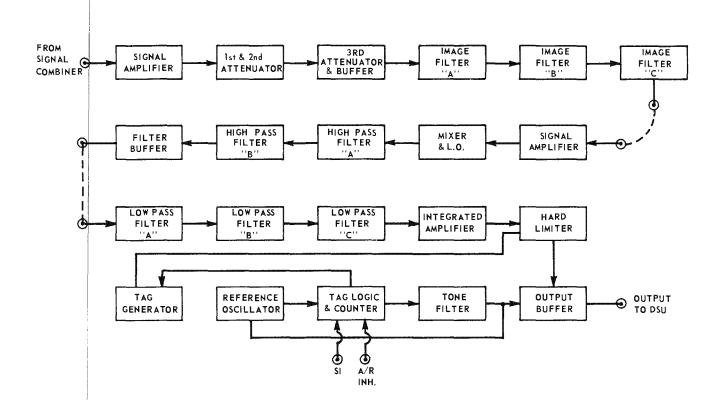

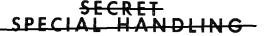

is achieved to fit the matched signal's amplitude into the vehicle recorder's useful dynamic range as shown in Figure 2.2-1. Two reference tones (46.875 kHz and 6.0 MHz) are added to the predetected output. Each signal not generating an amplitude ratio inhibit is followed by a tag pulse as a coarse sorting aid. Figure 2.2-2 illustrates the predetected bandwidth, tones and tag pulse characteristics.

FIGURE 2.2-1 PREDETECTOR AMPLITUDE RESPONSE CURVES

## SPECIAL HANDLING

52000-R500 Page 17

FIGURE 2.2-2 PREDETECTOR SIGNAL CHARACTERISTICS

SPECIAL HANDLING

approved for Release: 2017/08/16 C05099935

50X1

GEORGES CAS BARRAS CASAS

Page 18

#### 2.2.3 Marker Word

Digital marker words are output to the digital channel of the vehicle analog recorder to aid in sorting and identifying predetected signals. The marker words are generated at the rate of 8 per second synchronized to the vehicle clock and are output during the recording time after a match, or if the vehicle recorder is actuated. The marker word contains the data described in paragraph 2.4.2. The "Amplitude" Threshold" data specifies the predetected signal's amplitude characteristics (refer to Figure 2.2-1), the "Set ID" identifiles the stored set matched, and the "Frequency" corresponds to the local oscillator frequency.

#### 2.3 Operation

This section describes the system's operation in various commandable modes. The operational modes are summarized in Table 2.3-1. Table 2.3-4 contains a complete list of commands and associated "R" numbers. Tables 2.3-2 and 2.3-3 contain a brief summary of command restrictions. Each command function is described in detail below.

#### 2.3.1 EOB Readin

The Reaper system's normal data processing mode is described as "EOB Readin." Operation is controlled and may be modified by command as described in the following paragraphs.

50X1

MANDLE VIA BYEMAN CONTROL SYSTEM ONLY

# Approved for Release: 2017/08/16 C05099935

SPECIAL HANDLING

52000-R500 Page 19

TABLE 2.3-1 OPERATIONAL MODES\*

| MODE | OPERATION .                     |  |  |  |  |  |

|------|---------------------------------|--|--|--|--|--|

| 1.   | Normal (EOB) Data Processing    |  |  |  |  |  |

|      | "EOB READIN"                    |  |  |  |  |  |

| 2.   | Normal (EOB/TI) Data Processing |  |  |  |  |  |

|      | "EOB/TI READIN"                 |  |  |  |  |  |

| 3.   | Recognizer Memory Load          |  |  |  |  |  |

| 4.   | Partial Scan Memory Load        |  |  |  |  |  |

| 5.   | Memory Readout                  |  |  |  |  |  |

<sup>\*</sup>All operate mode commands, R13, R49, R61, R51, must be mutually exclusive.

TABLE 2.3-2 COMMAND RESTRICTION SUMMARY

| Function                            | Command              |

|-------------------------------------|----------------------|

| Partial Scan "A" On/Off             | (R3/R <sup>4</sup> ) |

| Partial Scan "B" On/Off             | (R59/R60)            |

| Disable Upper Frequency Band        | (R <b>1</b> 5)       |

| Disable Lower Frequency Band        | (R16)                |

| Enable Upper & Lower Frequency Band | (R17)                |

| Disable Memories (SWI & Buffer)     | (R18)                |

| Reset for Commands R18-R25          |                      |

| IF Memories Have Been Disabled      | (R26)                |

| Recognizer Enable/Disable           | (R9/R10)             |

|                                     |                      |

52000-R500 Page 20

TABLE 2.3-3 COMMANDS WITH NO RESTRICTIONS

| Function                         | Commands  |

|----------------------------------|-----------|

| Increase/Decrease Dwell Time     | (R1/R2)   |

| Disable FOV                      | (R19)     |

| Disable T <sub>min</sub> Confirm | (R2O)     |

| Disable T <sub>max</sub> Inhibit | (R21)     |

| Disable A/R Inhibit              | (R22)     |

| Disable Real/Image Confirm       | (R23)     |

| Disable Minimum PW Confirm       | (R24)     |

| Disable Frequency Confirm        | (R25)     |

| Enable/Disable CW-SI Ckt.        | (R27/R28) |

| Time Reset                       | (R58)     |

| Enable/Disable Recognizer Buffer | (R30/R29) |

- 2.3.1.1 EOB Readin Command Functions and Restrictions

- 2.3.1.1.1 Payload On (R11)

Function - This command actuates the system primary power supply to supply power supply to supply power to all circuits not supplied from the auxiliary power supply. Recognizer Enable (R9) must be issued to supply power to recognition circuits.

Restrictions - All operate modes (Readin, Recognizer input, Partial Scan Input, and Recognizer Partial Scan Readout) shall be disabled before

CONTROL SYSSEM ONLY

#### TABLE 2.3-4. SYSTEM COMMANDS

|                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Increase Dwell Time Decrease Dwell Time Partial Frequency Scan A On Partial Frequency Scan A Off Threshold Control A Threshold Control B | R29<br>R30<br>R31<br>R32<br>R33<br>R34<br>R35                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Disable Recognizer Buffer<br>Enable Recognizer Buffer<br>Enable RF Calibrator<br>Disable RF Calibrator<br>Enable Set A<br>Disable Set A<br>Enable Set B                                                                                                                                                                                                                                                                                                                                                               |

| Recognizer Enable<br>Recognizer Disable<br>Payload On<br>Payload Off                                                                     | R37<br>R38<br>R39<br>R40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Disable Set B Enable Set C Disable Set C Enable Set D Disable Set D Enable Set E                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Readin Off  Readin Off  Disable Upper Frequency Band  Disable Lower Frequency Band  Enable Upper & Lower Frequency  Band                 | R42<br>R43<br>R44<br>R45<br>R46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Disable Set E Enable Set F Disable Set F Enable Set G Disable Set G                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Disable Memories Disable FOV Inhibit Disable Tmin Confirm Disable Tmax Inhibit Disable A/R Inhibit                                       | R47<br>R48<br>R49<br>R50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Enable Set H Disable Set H Enable Recognizer Input Mode Disable Recognizer/Partial                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Disable P.W. Confirm Disable Frequency Confirm Reset R18 through R25 Disable C.W S.I.                                                    | R51<br>R52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Scan Input Mode Enable Recognizer/Partial Scan Readout Disable Recognizer/Partial Scan Readout Recognizer Threshold Bit A                                                                                                                                                                                                                                                                                                                                                                                             |

| _                                                                                                                                        | Decrease Dwell Time Partial Frequency Scan A On Partial Frequency Scan A Off Threshold Control A Threshold Control B Threshold Control B Threshold Control B Recognizer Enable Recognizer Disable Payload On Payload Off Readin On Readin Off Disable Upper Frequency Band Disable Lower Frequency Band Enable Upper & Lower Frequency Band Disable Memories Disable FOV Inhibit Disable Tmin Confirm Disable A/R Inhibit Disable Real/Image Confirm Disable P.W. Confirm Disable Frequency Confirm Reset R18 through R25 | Decrease Dwell Time Partial Frequency Scan A On Partial Frequency Scan A Off R32 Threshold Control A R34 Threshold Control B R35 Threshold Control B R36 Recognizer Enable R37 Recognizer Disable Payload On Payload Off Readin On Readin Off Disable Upper Frequency Band Disable Lower Frequency Band Enable Upper & Lower Frequency Band Disable Memories Disable FOV Inhibit Disable Tmin Confirm Disable A/R Inhibit Disable Real/Image Confirm Disable Frequency Confirm Reset R18 through R25 Disable C.W S.I. |

SECRET

SPECIAL HANDLING

Approved for Release: 2017/08/16 C05099935

CONTROL SYSTEM ONLY

Approved for Release: 2017/08/16 C05099935

50X1

TATOLE VIL BYCHAM

#### Approved for Release: 2017/08/16 C05099935 <del>HANDLING</del>

52000-R500 Page 23

issuing Rll. After issuing Rll. a minimum delay of one second shall be provided before enabling the payload in any operate mode.

#### 2.3.1.1.2 Payload Off (R12)

Function - P/L OFF Command deactuates the primary power supply.

Restrictions - All operate modes shall have been OFF for a minimum of 500 milliseconds before issuing Payload-OFF Command.

#### 2.3.1.1.3 Increase Dwell Time (R1)